## Technologie et Physique de Transistors Bipolaires à Hétérojonction Si/SiGeC Auto-alignés très Hautes Fréquences

Benoit Barbalat

#### ▶ To cite this version:

Benoit Barbalat. Technologie et Physique de Transistors Bipolaires à Hétérojonction Si/SiGeC Autoalignés très Hautes Fréquences. Micro et nanotechnologies/Microélectronique. Université Paris Sud-Paris XI, 2006. Français. tel-00139028

#### HAL Id: tel-00139028

https://tel.archives-ouvertes.fr/tel-00139028

Submitted on 20 Dec 2007

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N° D'ORDRE: 8571

## UNIVERSITÉ PARIS-SUD XI

## Faculté des Sciences d'Orsay

#### THÈSE DE DOCTORAT

SPÉCIALITÉ: PHYSIQUE

École Doctorale « Sciences et Technologies de l'Information des Télécommunications et des Systèmes »

Présentée par :

#### Benoît BARBALAT

Titre:

# Technologie et Physique de Transistors Bipolaires à Hétérojonction Si/SiGeC Auto-alignés très Hautes Fréquences

Soutenue le 22 décembre 2006 devant les membres du jury :

Pr. Frédéric Aniel Directeur de thèse Pr. Peter Ashburn Rapporteur

Dr. Pascal Chevalier Responsable de thèse

Pr. François Danneville Examinateur

Dr. Sylvain Delage Rapporteur

Pr. Robert Plana Président du jury

Dr. Alain Chantre Invité

Dr. Nicolas Zerounian Invité

Étudiez comme si vous deviez vivre toujours, Vivez comme si vous deviez mourir demain. Saint Isidore de Séville

## Remerciements

Le travail de thèse que vous tenez entre les mains est le fruit d'une collaboration entre STMicroelectronics Crolles et l'Institut d'Electronique Fondamentale (IEF) de l'Université Paris-Sud Orsay. J'ai pu naviguer entre les deux structures d'accueil, tout en bénéficiant d'un tutorat motivant et passionné, ce qui a été extrêmement formateur. A ce titre, je tiens à remercier tout particulièrement les personnes qui m'ont encadré durant ces trois ans :

Je remercie tout d'abord Pascal Chevalier de STMicroelectronics, qui m'a permis de réaliser ce travail de thèse dans d'excellentes conditions. Merci pour m'avoir si vite laissé la main sur des projets de recherche, et pour les nombreuses publications que nous avons co-écrites.

Je tiens à remercier également Nicolas Zerounian, de l'IEF, pour les longues discussions que nous avons pu avoir sur le fonctionnement du composant. Merci également pour ton soutien et ton aide dans les mesures cryogéniques (parfois jusque tard le soir!).

Je remercie sincèrement Alain Chantre, chef d'orchestre de l'équipe «Bipavancés» de ST, pour l'appui qu'il m'a apporté au cours de la thèse. Merci pour ton soutien et la confiance que tu m'as apportés dans la réalisation des différents projets qui m'ont été confiés.

J'adresse mes plus profonds remerciements à Frédéric Aniel, qui a été mon directeur de thèse. Merci pour tes excellents conseils tout au long de ces trois années, et pour avoir su m'orienter lorsque j'en avais besoin.

Je tiens à remercier les rapporteurs et examinateurs de ce travail, Peter Ashburn, Sylvain Delage, Robert Plana et François Danneville pour avoir accepté de participer à ce jury de thèse, ainsi que pour le travail de relecture et d'évaluation qu'ils ont fourni.

L'étude des transistors bipolaires à hétérojonction n'est possible que si l'on a des transistors bipolaires à hétérojonction. Je tiens donc à remercier les différentes équipes de ST avec qui nous interagissons tous les jours pour réaliser des structures de TBH toutes plus complexes les unes que les autres...

Citons tout d'abord, l'équipe de Front-End Of Line R&D, dirigée par Didier Dutartre : Merci à Benoît Vandelle et Laurent Rubaldo, maîtres incontestés de l'HTF, pour la qualité des nombreux dépôts réalisés. Petite pensée aux anciens membres l'équipe FEOL, Cyril Fellous, Alexandre Talbot et Benjamin Oudet, partis vers des horizons plus ou moins lointains...

Je tiens à remercier Fabienne Judong et Claire Richard de l'équipe Patterning, pour leur disponibilité et les nombreux essais de gravure que nous avons réalisés.

Merci à Pierre Bouillon pour avoir pris soin de nos composants le week-end, lors d'étapes de photolithographie délicates.

Je remercie aussi Marina Proust et Pierre Caubet de l'équipe Métal, pour leur disponibilité, et avoir fait de l'émetteur métallique une réalité qui marche!

La réalisation des composants est une chose; l'étude, l'analyse et la compréhension des phénomènes en est une autre. A ce titre, je tiens à remercier les équipes de caractérisation physique et électrique, de simulation et de modélisation, qui soutiennent largement le travail de la filière. Je remercie tout particulièrement :

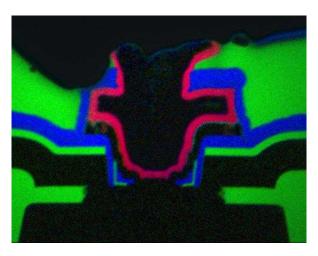

- Roland Pantel, Nadine Bicaïs, David Duca, Alain Margain, de l'équipe caractérisation physique, pour la qualité des nombreuses analyses qu'ils nous ont fournies.

- Fabienne Saguin et Daniel Gloria, pour les innombrables mesures hyperfréquences qui soutiennent ce travail de thèse. Les résultats fournis ont été plus que précieux tout au long de ces trois années.

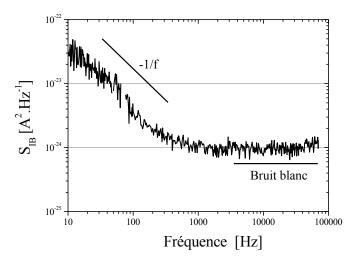

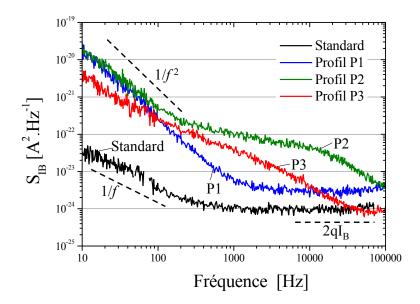

- Jean-Charles Vildeuil et Anne Lachater, pour les mesures de bruit 1/f menées sur nos composants, et l'attention apportée à nos demandes.

- Thierry Schwartzmann, pour l'important travail de simulation réalisé, et la collaboration étroite que nous avons eue sur le sujet de la recombinaison en base neutre et de l'autoéchauffement.

- Didier Céli et Franck Pourchon, pour leur travail de modélisation. Merci tout particulièrement pour les habiles méthodes de mesure et d'extraction, qui ont été largement utilisées dans ce travail.

- La mise à disposition permanente des bancs de mesure statique est rendu possible par André Perrotin et Rudy Costanzi. Merci pour votre disponibilité et votre réactivité lorsque les systèmes de mesure tombent en panne (mais c'est rare).

Je tiens à adresser mes remerciements à Olivier Noblanc pour avoir toujours gardé un oeil sur moi durant mes quelques années passées à Crolles. Merci pour les longues discussions que nous avons eues, en stage, en thèse, ou ailleurs.

Il ne faudrait pas non plus croire que je n'ai fait *que* travailler durant trois ans. Aussi je tiens à remercier les nombreux thésards qui ont contribué à la bonne humeur ambiante, dans les couloirs ou dans un pub irlandais célèbre de la vallée du Grésivaudan. Citons notamment :

- Greg: *Rock On* toi même!

- Dorothée, la iPod-Girl

- Stéphane, avec qui nous avons passé de nombreuses heures sur les subtilités de LATEX

- Carlo: BSC rules!

- Aurélie : Comment faire aboyer un chat ? On l'enduit d'essence, on allume et "Wouaf"!

- Ceux qui sont encore dedans : Julien, Pierre-Marie et Boris. Bon courage pour la rédaction !

Les doctorants des autres équipes sont trop nombreux pour être tous cités. Je voudrais néanmoins être sûr de ne pas oublier :

- Flo, Nico et Gaël, pour les bons moments dans le New-Jersey.

- Helène : DT rules !

- Antoine, Bastien, Olivier, Axel, Siegfried, Nathalie, Marie, et toutes celles et ceux avec qui j'ai partagé de bons moments.

Un remerciement spécial à Luc avec qui je partage la même passion pour la musique. Que ce projet que nous montons tous les deux vive encore de longues années...

Puis merci à tous les membres de l'équipe R&D de Crolles 1 ou 2, Mertrand Bartinet, Dominik, Sébastien (×2), Michel (×2), Stéphanie, Laurence, Jocelyne, Germaine, Emmanuelle, Isabelle, Simon, pour les looongues pauses café...

Bonne continuation à tous!

J'ai passé ces trois années bien entouré par de vieux copains qui font presque partie de la famille maintenant. Aussi je tiens à remercier Jérôme, Alex, Rod, Jean-François, les potes de la promo 2003, la famille Molo, les JEM d'Inde 2002. Vous avez été largement responsables du maintien de ma bonne santé mentale, et je vous en remercie!

Je remercie également la famille proche, et en particulier mes grand-parents, qui ont su me communiquer cet amour de la science, et qui se sont toujours montrés intéressés par mes recherches. Merci pour votre chaleureuse attention, et votre soutien. Je vous dédie cette thèse.

Merci à frérot et sœurette, bon courage pour la suite de vos études à vous!

Je remercie également mes parents, qui ont largement contribué à faire de moi ce que je suis aujourd'hui. Je ne pourrais jamais leur communiquer assez ma reconnaissance et ma gratitude à leur égard.

Mes dernières pensées vont à Mélanie, ma fiancée. Merci pour ton soutien, tes encouragements, ta complicité. A jamais, tu resteras pour moi associée à la réussite de cette thèse.

## Table des matières

| I | Le t | ransisto | r bipolaire à hétérojonction Si / SiGeC                                     | 5 |

|---|------|----------|-----------------------------------------------------------------------------|---|

|   | I.1  | Introdu  | action sur le transistor bipolaire                                          | 5 |

|   | I.2  | L'allia  | ge Silicium-Germanium                                                       | 8 |

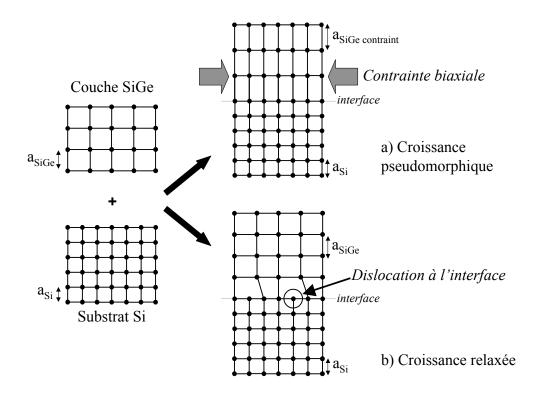

|   |      | I.2.1    | 1                                                                           | 8 |

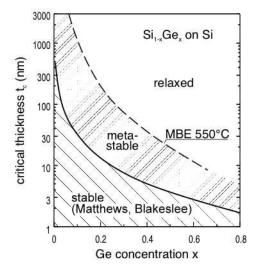

|   |      |          | I.2.1.a Paramètre de maille et caractéristiques de la couche                | 8 |

|   |      |          | I.2.1.b Épaisseur critique                                                  | 8 |

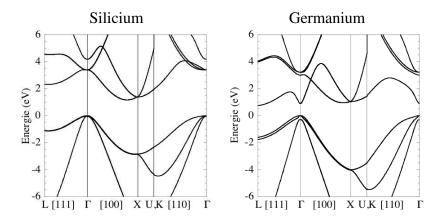

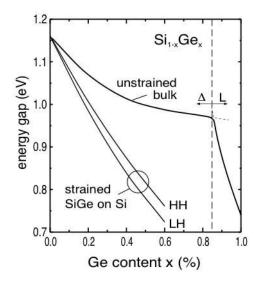

|   |      |          | I.2.1.c Influence des contraintes mécaniques sur le diagramme de            |   |

|   |      |          | bandes                                                                      | 0 |

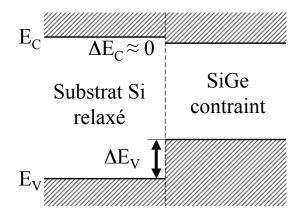

|   |      | I.2.2    | Hétérojonction Si / SiGe                                                    | 0 |

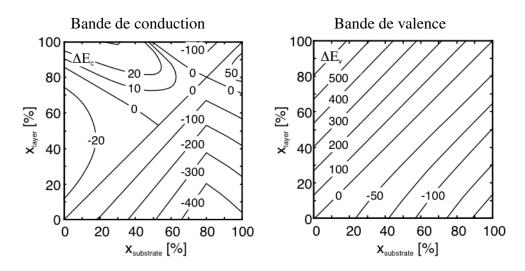

|   |      |          | I.2.2.a Raccordement des bandes                                             | 0 |

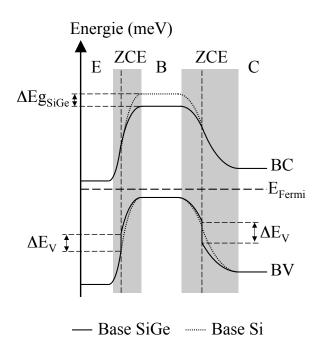

|   |      |          | I.2.2.b Structure électronique d'un transistor bipolaire à hétérojonction 1 |   |

|   |      |          | I.2.2.c Introduction de carbone                                             |   |

|   |      |          | I.2.2.c.i Incorporation en site interstitiel ou substitutionnel . 1         |   |

|   |      |          | I.2.2.c.ii Modification de la structure de bande                            |   |

|   | I.3  |          | onnement statique du transistor bipolaire                                   |   |

|   |      | I.3.1    | Bilan des différents courants du transistor                                 |   |

|   |      | I.3.2    | Expression des courants                                                     |   |

|   |      |          | I.3.2.a Équations fondamentales                                             |   |

|   |      |          | I.3.2.b Courant collecteur                                                  |   |

|   |      |          | I.3.2.b.i Cas général sans recombinaison                                    |   |

|   |      |          | I.3.2.b.ii Cas avec recombinaison dans une base uniforme 1                  |   |

|   |      |          | I.3.2.b.iii Discussion                                                      |   |

|   |      |          | I.3.2.c Courant de base                                                     |   |

|   |      | I.3.3    | Différents gains en courant                                                 |   |

|   |      |          | I.3.3.a Montage base commune                                                |   |

|   |      |          | I.3.3.b Montage émetteur commun                                             |   |

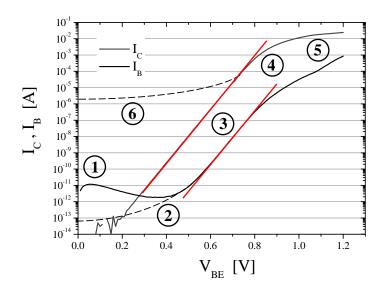

|   |      | I.3.4    | Effets du second ordre                                                      |   |

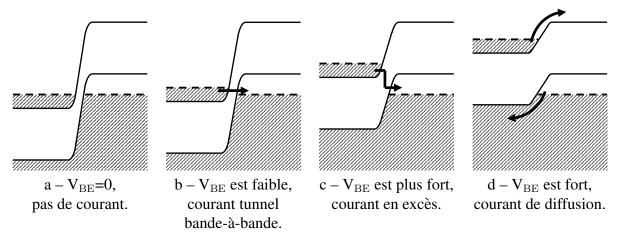

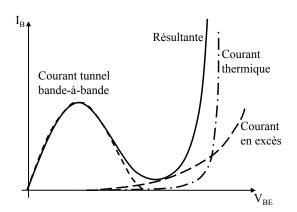

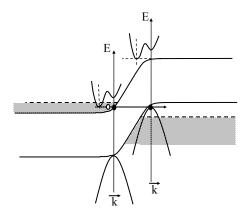

|   |      |          | I.3.4.a Courants non-idéaux à faible polarisation                           |   |

|   |      |          | I.3.4.a.i Recombinaison en zone de charge d'espace 2                        |   |

|   |      |          | I.3.4.a.ii Courant tunnel bande à bande                                     |   |

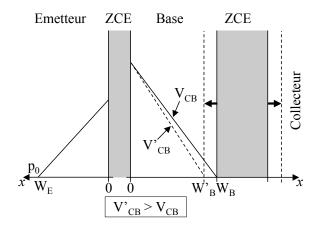

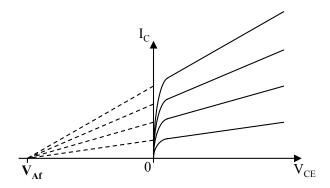

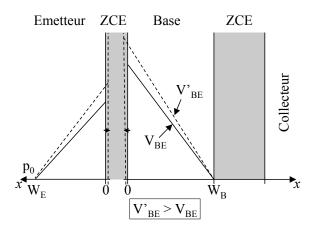

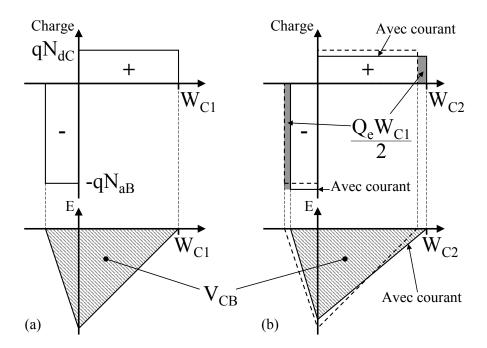

|   |      |          | I.3.4.b Effet Early                                                         |   |

|   |      |          | I.3.4.b.i Effet Early direct                                                |   |

|   |      |          | I.3.4.b.ii Effet Early inverse                                              |   |

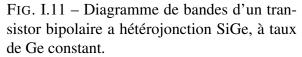

|   |      |          | I.3.4.b.iii Influence du profil graduel de SiGe                             |   |

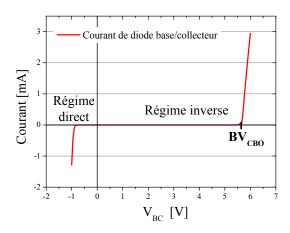

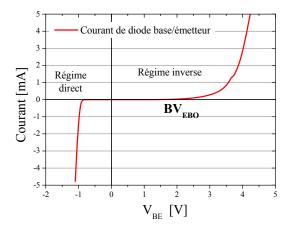

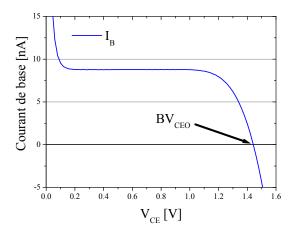

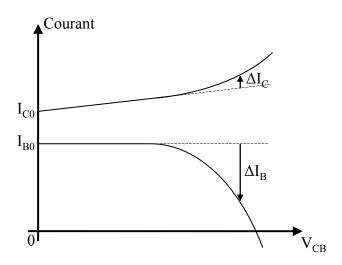

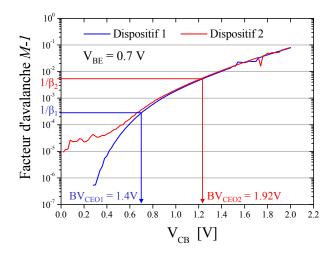

|   |      |          | I.3.4.c Tensions d'avalanche                                                |   |

|   |      |          | I.3.4.c.i Définition et caractérisation de l'avalanche 2                    |   |

|   |      |          | I.3.4.c.ii $BV_{CBO}$                                                       |   |

|   |      |          | I.3.4.c.iii $BV_{EBO}$                                                      |   |

|   |      |          | I.3.4.c.iv $BV_{CEO}$                                                       | 9 |

|     |         | I.3.4.d    | Effet de haute injection dans la base (effet Webster) | 31 |

|-----|---------|------------|-------------------------------------------------------|----|

|     |         | I.3.4.e    | Effet Kirk                                            | 31 |

|     |         | I.3.4.f    | Effet de barrière                                     | 32 |

|     | I.3.5   | Effet des  | s forts dopages                                       | 32 |

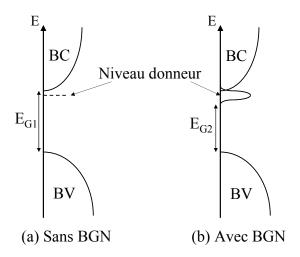

|     |         | I.3.5.a    | Réduction de bande interdite                          | 33 |

|     |         | I.3.5.b    | Modification des équations des courants               | 33 |

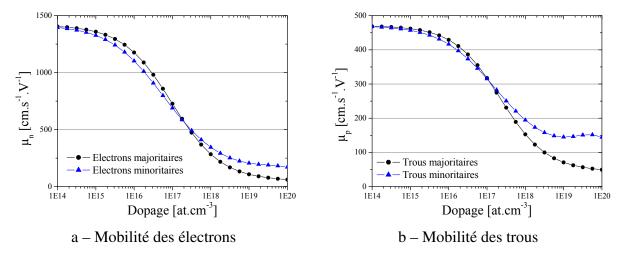

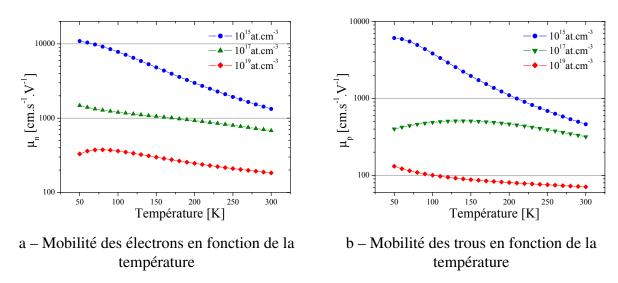

|     |         | I.3.5.c    | Mobilité des porteurs                                 | 34 |

| I.4 | Foncti  | onnement   | dynamique du transistor bipolaire                     | 36 |

|     | I.4.1   |            | le transit des porteurs                               |    |

|     |         | I.4.1.a    | Temps de transit émetteur                             | 37 |

|     |         | I.4.1.b    | Temps de transit dans la jonction émetteur/base       | 38 |

|     |         | I.4.1.c    | Temps de transit dans la base                         | 38 |

|     |         | I.4.1.d    | Temps de transit dans la jonction base/collecteur     | 39 |

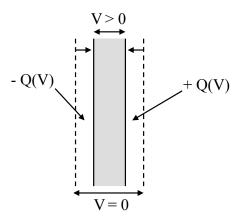

|     | I.4.2   | Capacité   | és de jonction                                        | 41 |

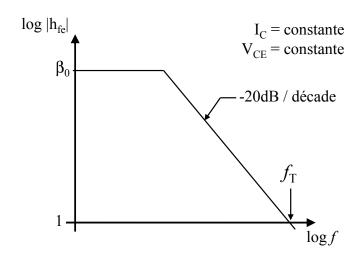

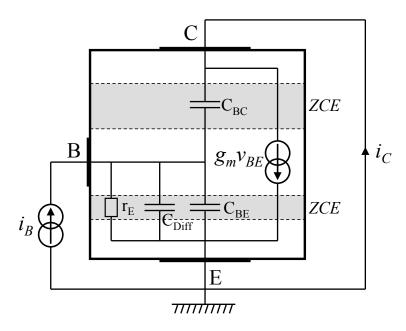

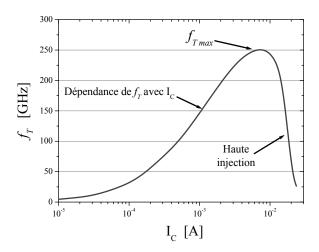

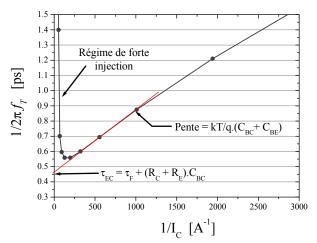

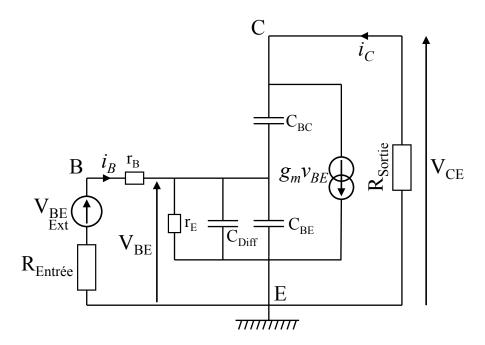

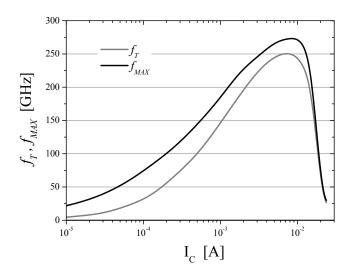

|     | I.4.3   |            | ces de transition $f_T$ et $f_{MAX}$                  |    |

|     |         | I.4.3.a    | Définition et expression de $f_T$                     |    |

|     |         | I.4.3.b    | Expression de $f_{MAX}$                               |    |

| I.5 | Effet o | des basses | températures                                          | 46 |

|     | I.5.1   |            | tement statique à basses températures                 |    |

|     | I.5.2   | Influenc   | e sur les performances dynamiques                     | 48 |

|     | I.5.3   | Un outil   | d'anticipation                                        | 49 |

| I.6 | Métho   | des de car | actérisation                                          | 49 |

|     | I.6.1   | Caractér   | isation physique                                      | 49 |

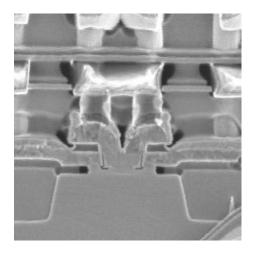

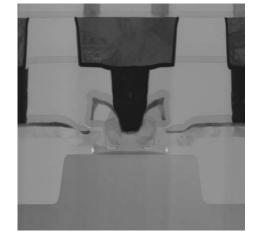

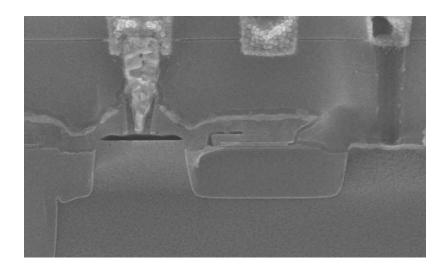

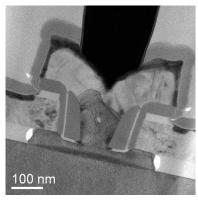

|     |         | I.6.1.a    | Microscope électronique à balayage (MEB)              | 49 |

|     |         | I.6.1.b    | Microscope électronique à transmission (MET)          | 49 |

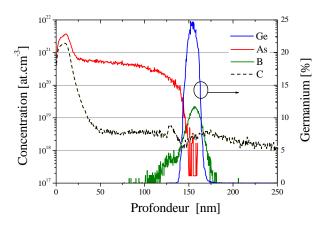

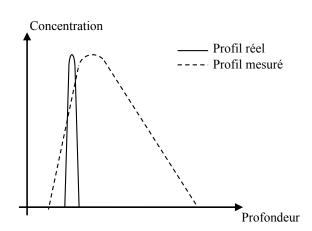

|     |         | I.6.1.c    | Spectroscopie de masse par ions secondaires           | 49 |

|     | I.6.2   | Mesures    | électriques en régime statique                        | 51 |

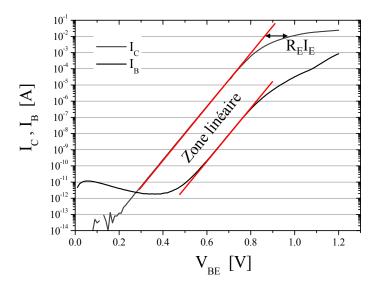

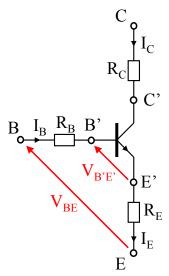

|     |         | I.6.2.a    | Idéalité, résistance d'émetteur                       | 51 |

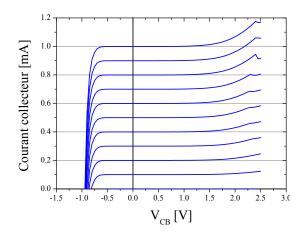

|     |         | I.6.2.b    | Caractérisation de l'avalanche dans la jonction B/C   | 51 |

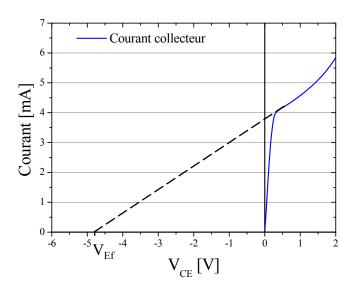

|     |         | I.6.2.c    | Mesure des tensions d'Early                           | 52 |

|     | I.6.3   | Hyperfre   | équences                                              | 54 |

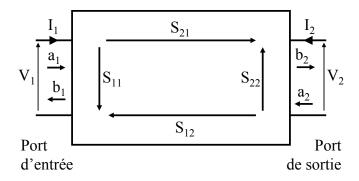

|     |         | I.6.3.a    | Intérêt des mesures de paramètres S                   | 54 |

|     |         | I.6.3.b    | Méthode d'analyse                                     | 54 |

|     |         | I          | .6.3.b.i Adaptation                                   |    |

|     |         | I          | .6.3.b.ii Calibrage                                   | 55 |

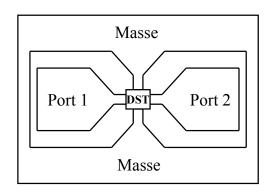

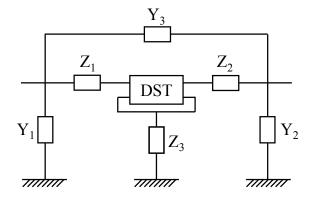

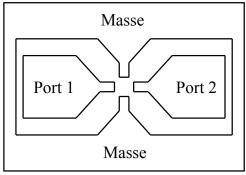

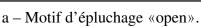

|     |         | I          | .6.3.b.iii Épluchage                                  | 56 |

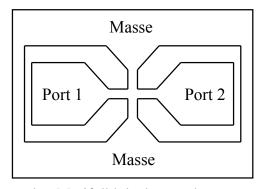

|     |         | I.6.3.c    | Extraction des différents paramètres                  | 57 |

|     |         | I.6.3.d    | Mesures hyperfréquences à basses températures         | 58 |

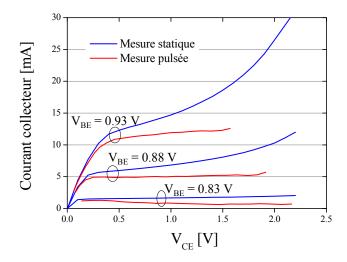

|     | I.6.4   | Régime     | impulsionnel                                          | 58 |

|     |         | I.6.4.a    | Intérêt des mesures pulsées (isothermes)              | 58 |

|     |         | I.6.4.b    | Mesures pulsées dynamiques                            | 59 |

|     | I.6.5   | Mesures    | de bruit                                              | 59 |

|     |         | I.6.5.a    | Bruit en $1/f$                                        | 60 |

|     |         | I.6.5.b    | Bruit haute fréquence                                 |    |

| I.7 | Applic  | cations    |                                                       | 61 |

|     | I.7.1   | Avantag    | es du transistor bipolaire par rapport au MOS         | 61 |

|     | I.7.2   |            | on dans le domaine des hautes fréquences              |    |

| II | Tech  | nologie                        | et fabrication des TBH SiGe                               | 63  |  |  |  |

|----|-------|--------------------------------|-----------------------------------------------------------|-----|--|--|--|

|    | II.1  | Introdu                        | action                                                    | 63  |  |  |  |

|    | II.2  | Structu                        | res non auto-alignées développées dans le passé           | 63  |  |  |  |

|    |       | II.2.1                         | Structure simple polysilicium                             | 63  |  |  |  |

|    |       | II.2.2                         | Structure double polysilicium                             | 64  |  |  |  |

|    | II.3  | Dévelo                         | ppement d'une structure complètement auto-alignée         | 66  |  |  |  |

|    |       | II.3.1                         | Nécessité d'une structure complètement auto-alignée       | 66  |  |  |  |

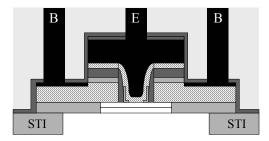

|    |       | II.3.2                         | Structure auto-alignée par émetteur sacrificiel           | 67  |  |  |  |

|    |       |                                | II.3.2.a Présentation de la structure inverse émetteur    | 67  |  |  |  |

|    |       |                                | II.3.2.b Procédé de fabrication                           | 67  |  |  |  |

|    |       |                                | II.3.2.c Avantages / Inconvénients                        | 68  |  |  |  |

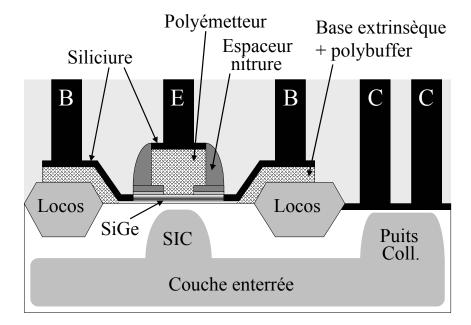

|    |       | II.3.3                         | Structure auto-alignée par épitaxie sélective de la base  | 68  |  |  |  |

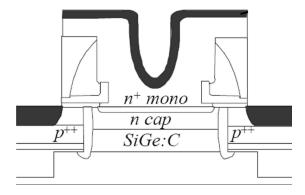

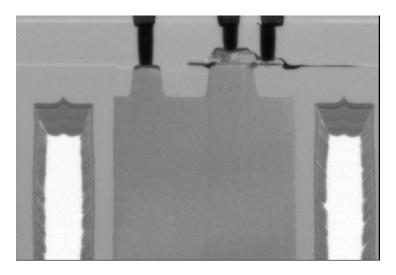

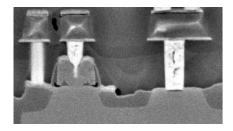

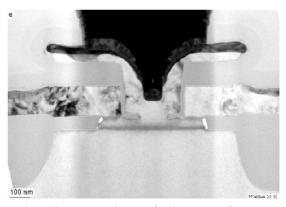

|    |       |                                | II.3.3.a Auto-alignement émetteur-base-collecteur         | 69  |  |  |  |

|    |       |                                | II.3.3.b Epitaxie sélective de la base                    | 70  |  |  |  |

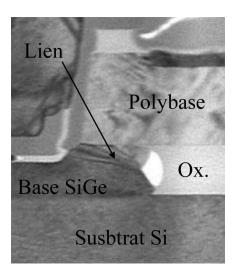

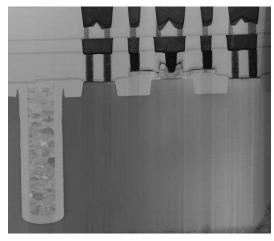

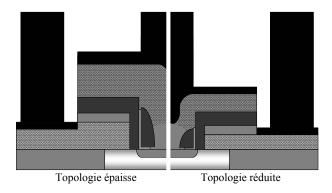

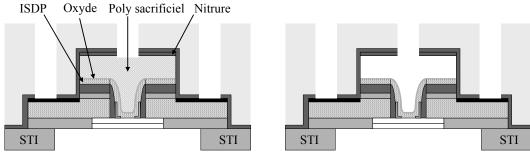

|    |       |                                | II.3.3.c Enchaînement des étapes de fabrication           | 70  |  |  |  |

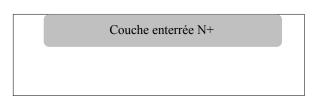

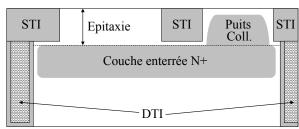

|    |       |                                | II.3.3.c.i Couche enterrée – Isolation                    | 71  |  |  |  |

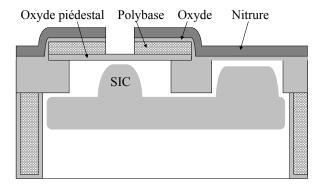

|    |       |                                | II.3.3.c.ii Base extrinsèque – Fenêtre émetteur           | 71  |  |  |  |

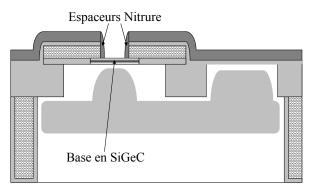

|    |       |                                | II.3.3.c.iii Base intrinsèque                             | 71  |  |  |  |

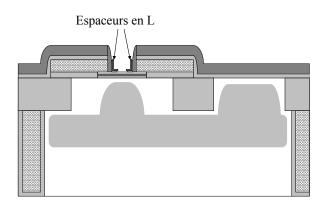

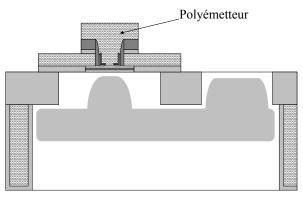

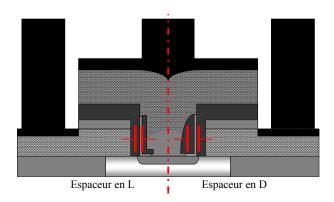

|    |       |                                | II.3.3.c.iv Espaceurs – Module émetteur                   | 73  |  |  |  |

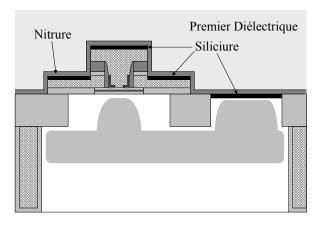

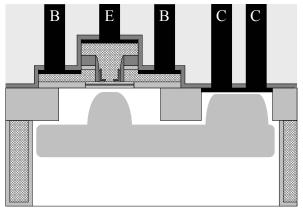

|    |       |                                | II.3.3.c.v Recuit d'activation – Siliciuration – Back-End | 73  |  |  |  |

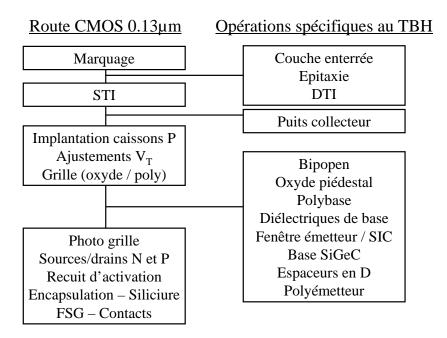

|    |       | II.3.4                         | Mise en place de la technologie BiCMOS                    | 74  |  |  |  |

|    |       |                                | II.3.4.a Enjeux de l'intégration                          |     |  |  |  |

|    |       |                                | II.3.4.b Schéma d'intégration BiCMOS                      | 75  |  |  |  |

|    | II.4  | Compa                          | araison par rapport à la concurrence                      | 76  |  |  |  |

|    |       | II.4.1                         | NXP (anciennement Philips)                                | 76  |  |  |  |

|    |       | II.4.2                         | IMEC                                                      | 76  |  |  |  |

|    |       | II.4.3                         | IHP                                                       | 77  |  |  |  |

|    |       | II.4.4                         | Jazz                                                      | 78  |  |  |  |

|    |       | II.4.5                         | Freescale (anciennement Motorola)                         | 78  |  |  |  |

|    |       | II.4.6                         | Hitachi                                                   | 78  |  |  |  |

|    |       | II.4.7                         | Infineon                                                  | 79  |  |  |  |

|    |       | II.4.8                         | IBM                                                       | 80  |  |  |  |

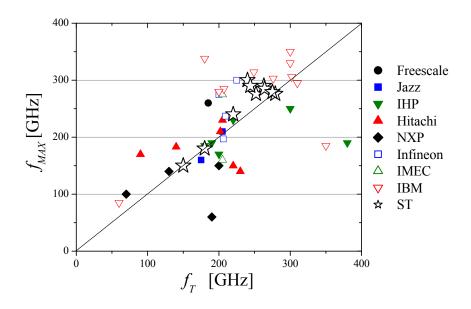

|    |       | II.4.9                         | Synthèse                                                  | 81  |  |  |  |

|    |       | • .•                           | d II I mpy                                                | 0.2 |  |  |  |

| Ш  | _     |                                | n conventionnelle du TBH                                  | 83  |  |  |  |

|    |       |                                | l'optimisation verticale et latérale                      | 83  |  |  |  |

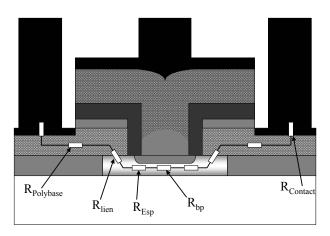

|    | 111.2 |                                | sation du module émetteur                                 | 83  |  |  |  |

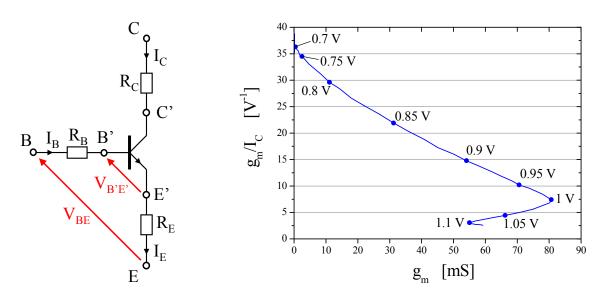

|    |       | 111.2.1                        | Mise en place d'une méthode d'extraction de $R_E$         | 85  |  |  |  |

|    |       |                                | III.2.1.a Méthode basée sur des mesures statiques         | 85  |  |  |  |

|    |       |                                | III.2.1.b Influence de la zone d'extraction               | 86  |  |  |  |

|    |       | 111 2 2                        | III.2.1.c Accord extraction statique / dynamique          | 86  |  |  |  |

|    |       | III.2.2                        | Effet des différentes variantes technologiques            | 87  |  |  |  |

|    |       |                                | III.2.2.a Effet du dopage du polysilicium                 | 87  |  |  |  |

|    |       |                                | III.2.2.a.i Type de dopage (Phosphore ou Arsenic)         | 87  |  |  |  |

|    |       |                                | III.2.2.a.ii Niveau de dopage                             | 88  |  |  |  |

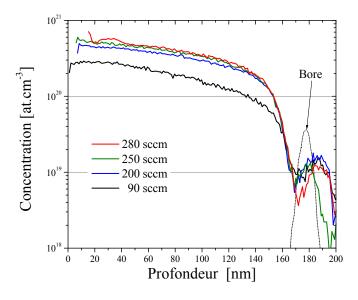

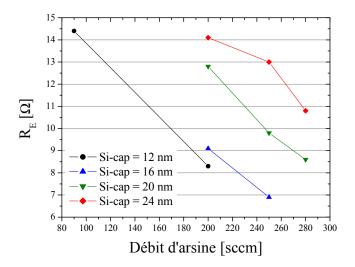

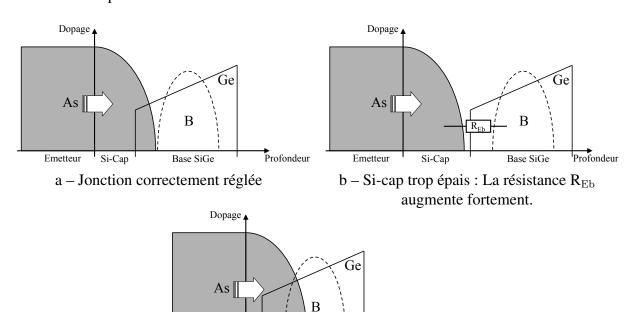

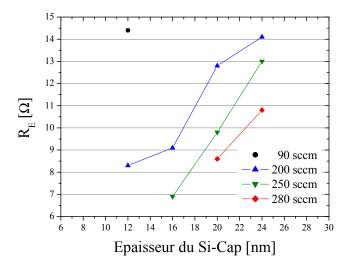

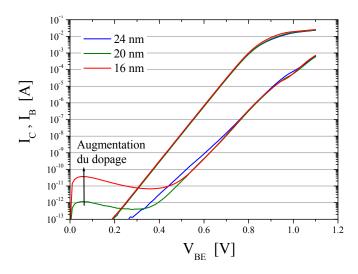

|    |       | 111 2 2                        | III.2.2.b Influence du Si-Cap                             | 90  |  |  |  |

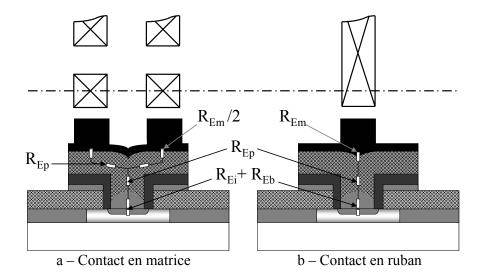

|    |       |                                | Effet de la géométrie du contact                          | 91  |  |  |  |

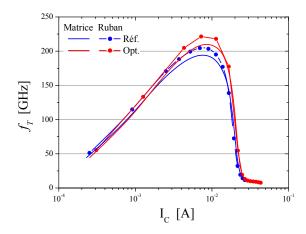

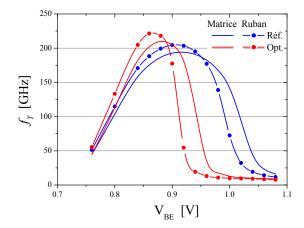

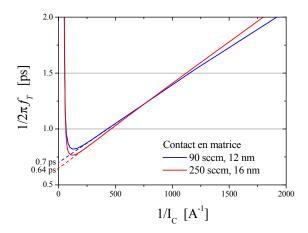

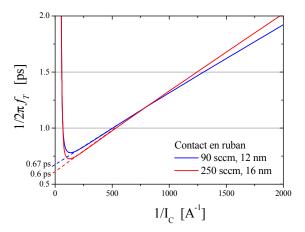

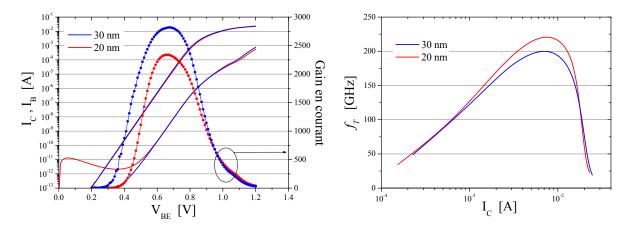

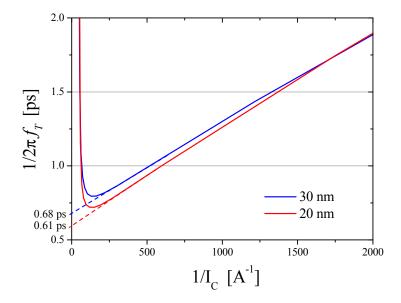

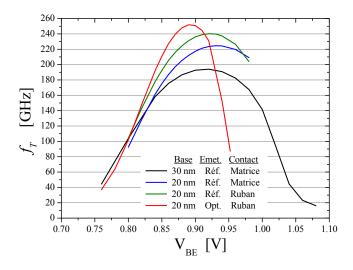

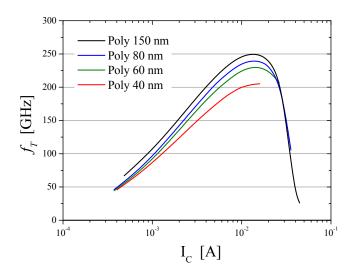

|    | 111.2 |                                | Gain sur les fréquences de transition                     | 92  |  |  |  |

|    | 111.3 | Optimisation du profil de base |                                                           |     |  |  |  |

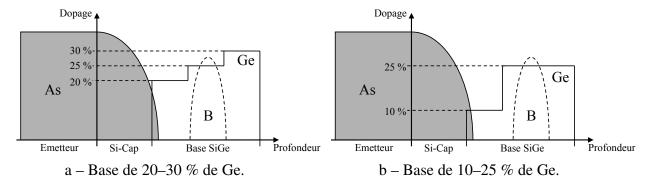

|    |       | III.3.1                                                  | Profils de germanium                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                         |  |  |

|----|-------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|

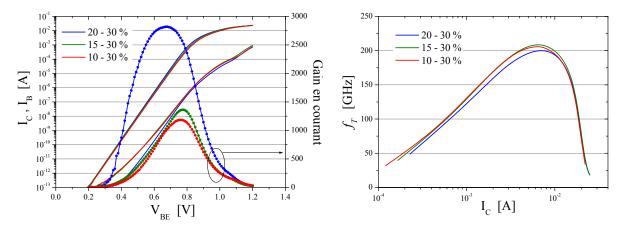

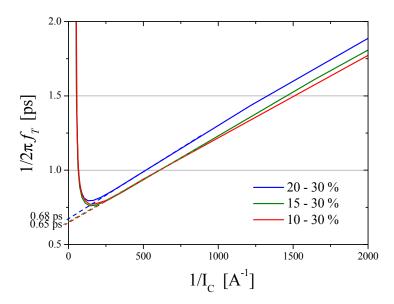

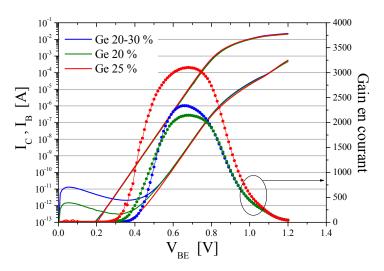

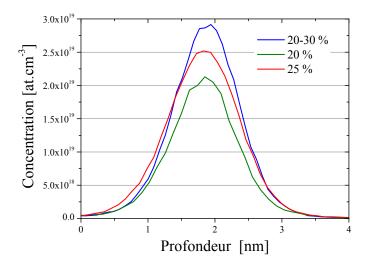

|    |       |                                                          | III.3.1.a Taux de Germanium à l'entrée de la base                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 96                                                                                      |  |  |

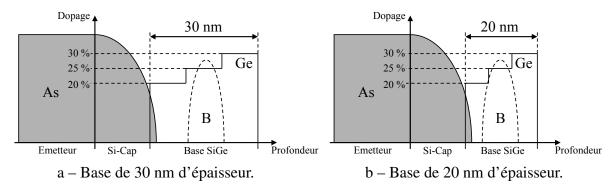

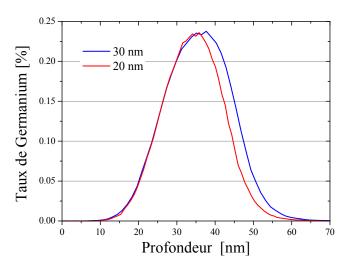

|    |       |                                                          | III.3.1.b Épaisseur de la couche de SiGe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 99                                                                                      |  |  |

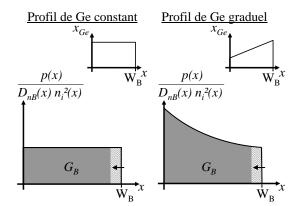

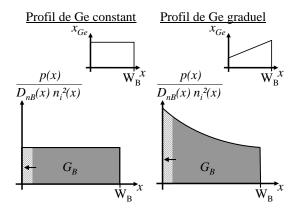

|    |       |                                                          | III.3.1.c Profil de Germanium graduel ou constant                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 101                                                                                     |  |  |

|    |       |                                                          | III.3.1.d Synthèse de l'optimisation du profil de base                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 102                                                                                     |  |  |

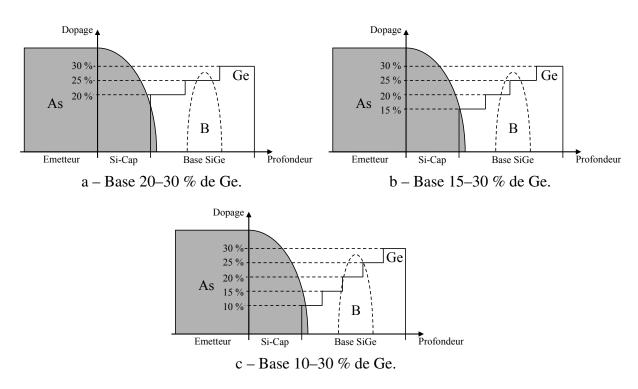

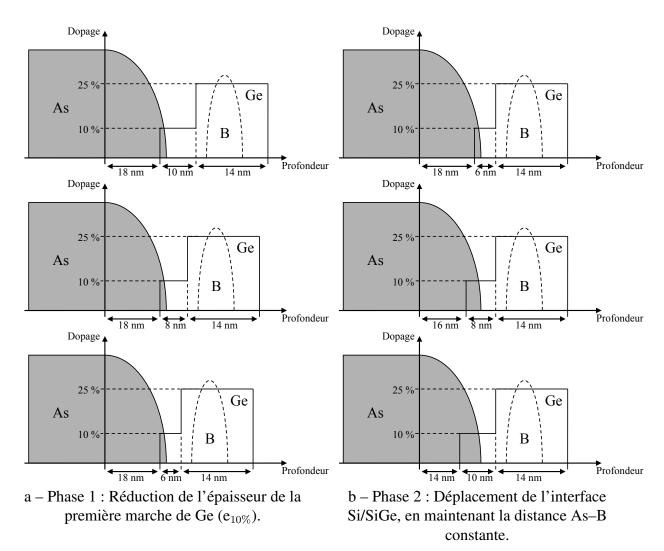

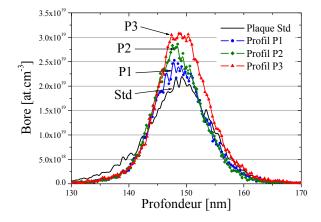

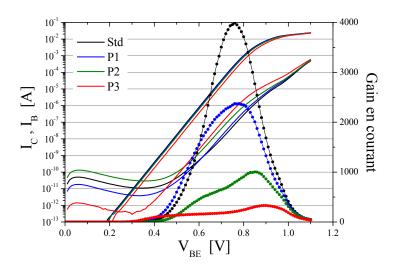

|    |       | III.3.2                                                  | Introduction d'un nouveau profil de base                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 103                                                                                     |  |  |

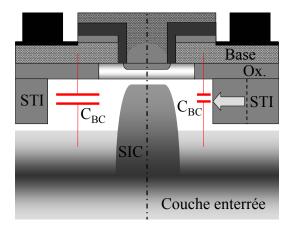

|    | III.4 |                                                          | sation du profil collecteur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 107                                                                                     |  |  |

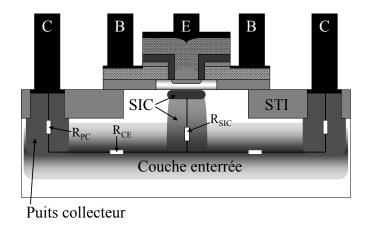

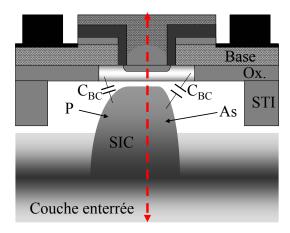

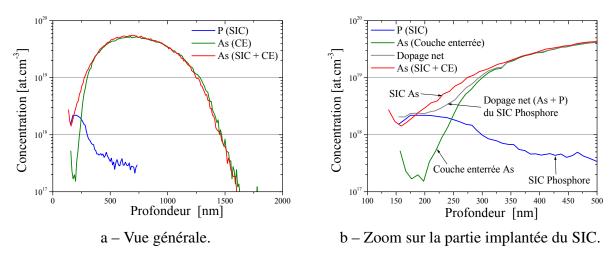

|    |       |                                                          | Collecteur implanté sélectivement (SIC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 107                                                                                     |  |  |

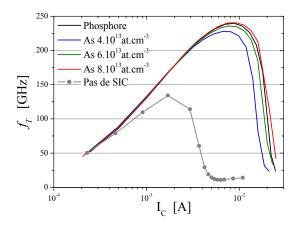

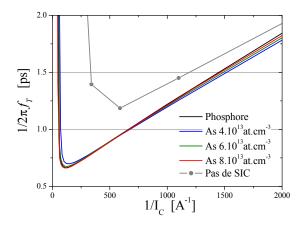

|    |       |                                                          | Résultats électriques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 108                                                                                     |  |  |

|    |       |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 109                                                                                     |  |  |

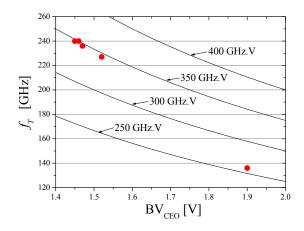

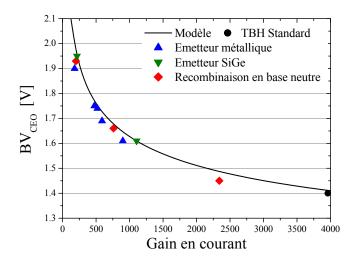

|    |       |                                                          | Compromis entre $f_T$ et $\mathrm{BV}_{\mathrm{CEO}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                         |  |  |

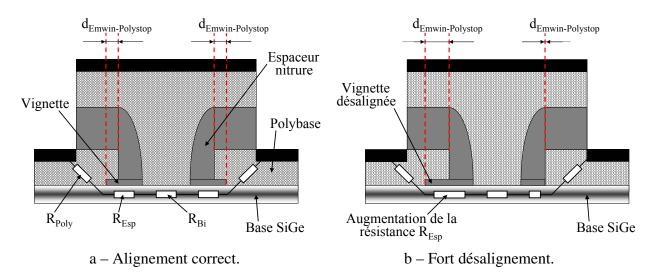

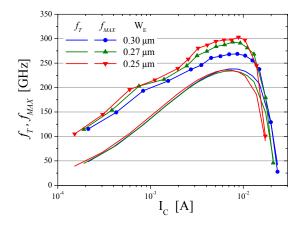

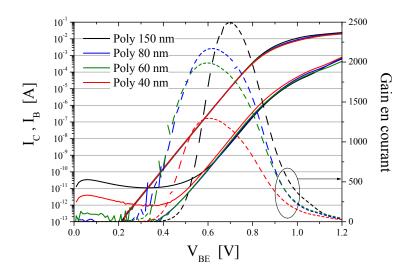

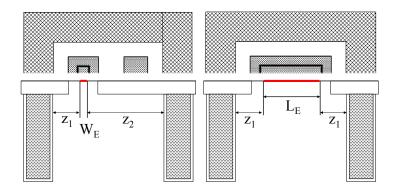

|    | III.5 |                                                          | tion des dimensions latérales du dispositif                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                         |  |  |

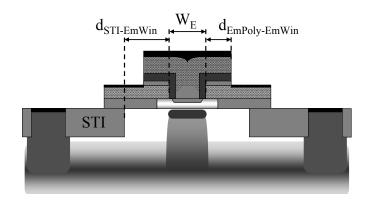

|    |       |                                                          | Largeur d'émetteur $W_E$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                         |  |  |

|    |       |                                                          | III.5.1.a Contact d'émetteur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                         |  |  |

|    |       |                                                          | III.5.1.b Largeur de la fenêtre émetteur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                         |  |  |

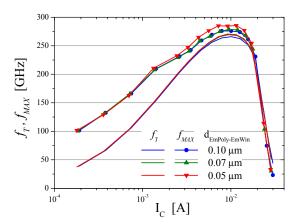

|    |       |                                                          | III.5.1.c Espaceurs internes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                         |  |  |

|    |       | III.5.2                                                  | Largeur de la zone d'active                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                         |  |  |

|    |       |                                                          | Largeur du polyémetteur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                         |  |  |

|    |       |                                                          | Synthèse de l'optimisation latérale.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                         |  |  |

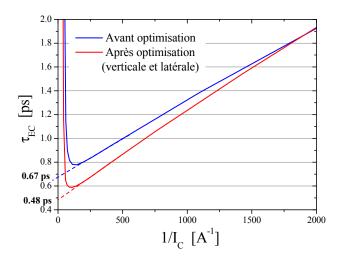

|    | III.6 |                                                          | se de l'optimisation conventionnelle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                         |  |  |

|    |       |                                                          | Performances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                         |  |  |

|    |       |                                                          | Développement d'une filière dédiée aux applications millimétriques                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                         |  |  |

|    |       |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                         |  |  |

| IV | Amé   | lioratio                                                 | on du produit $m{f}_T 	imes \mathbf{BV}_{\mathrm{CEO}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 121                                                                                     |  |  |

|    | IV.1  | Présent                                                  | tation de l'approche                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 121                                                                                     |  |  |

|    | IV.2  | Transis                                                  | stor bipolaire à émetteur métallique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 124                                                                                     |  |  |

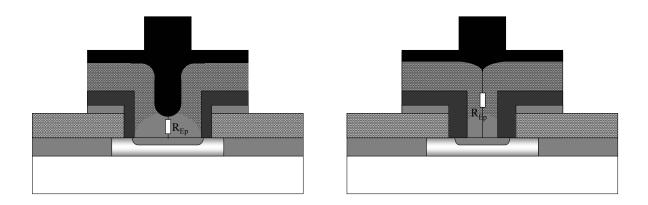

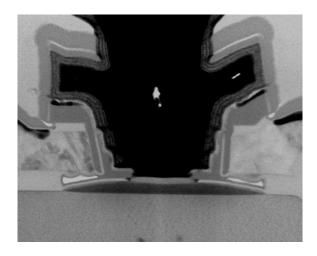

|    |       | IV.2.1                                                   | Réalisation technologique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 124                                                                                     |  |  |

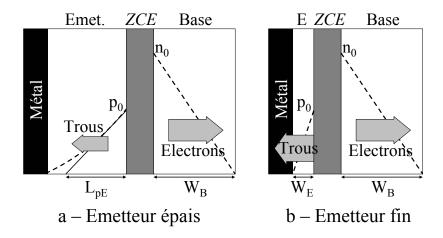

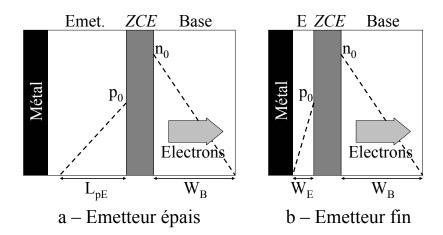

|    |       |                                                          | IV.2.1.a Architectures possibles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 124                                                                                     |  |  |

|    |       |                                                          | IV.2.1.b Détails du procédé PRETCH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 125                                                                                     |  |  |

|    |       | IV.2.2                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                         |  |  |

|    |       | 1 4.2.2                                                  | Résultats obtenus avec un émetteur fortement dopé                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 126                                                                                     |  |  |

|    |       | 1 4.2.2                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                         |  |  |

|    |       | 1 4.2.2                                                  | Résultats obtenus avec un émetteur fortement dopé                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 127                                                                                     |  |  |

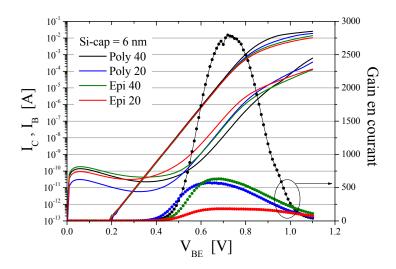

|    |       | 1 v.2.2                                                  | IV.2.2.a Résultats électriques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 127                                                                                     |  |  |

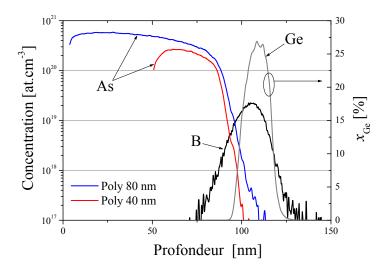

|    |       | 1 v.2.2                                                  | IV.2.2.aRésultats électriquesIV.2.2.bAnalyse SIMSIV.2.2.cMesures d'effet Hall                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 127<br>128                                                                              |  |  |

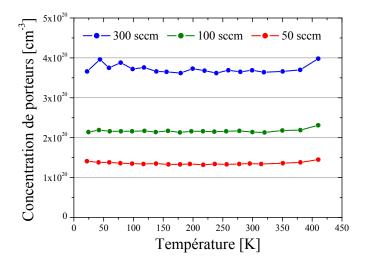

|    |       |                                                          | IV.2.2.aRésultats électriquesIV.2.2.bAnalyse SIMSIV.2.2.cMesures d'effet Hall                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 127<br>128<br>129                                                                       |  |  |

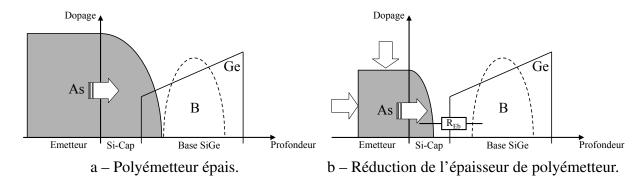

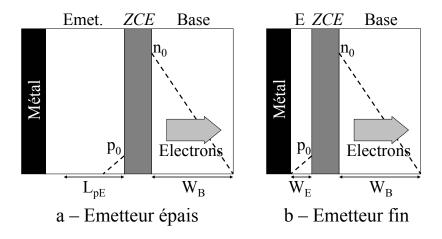

|    |       |                                                          | IV.2.2.a       Résultats électriques          IV.2.2.b       Analyse SIMS          IV.2.2.c       Mesures d'effet Hall          IV.2.2.d       Interprétation – Suite de l'étude          Résultats obtenus avec un émetteur faiblement dopé                                                                                                                                                                                                                                                                                    | 127<br>128<br>129<br>130                                                                |  |  |

|    |       |                                                          | IV.2.2.a       Résultats électriques          IV.2.2.b       Analyse SIMS          IV.2.2.c       Mesures d'effet Hall          IV.2.2.d       Interprétation – Suite de l'étude          Résultats obtenus avec un émetteur faiblement dopé                                                                                                                                                                                                                                                                                    | 127<br>128<br>129<br>130<br>130                                                         |  |  |

|    |       |                                                          | IV.2.2.a       Résultats électriques          IV.2.2.b       Analyse SIMS          IV.2.2.c       Mesures d'effet Hall          IV.2.2.d       Interprétation – Suite de l'étude          Résultats obtenus avec un émetteur faiblement dopé          IV.2.3.a       Résultats électriques                                                                                                                                                                                                                                      | 127<br>128<br>129<br>130<br>130<br>131                                                  |  |  |

|    | IV.3  | IV.2.3<br>IV.2.4                                         | IV.2.2.a       Résultats électriques         IV.2.2.b       Analyse SIMS         IV.2.2.c       Mesures d'effet Hall         IV.2.2.d       Interprétation – Suite de l'étude         Résultats obtenus avec un émetteur faiblement dopé         IV.2.3.a       Résultats électriques         IV.2.3.b       Problème d'augmentation des résistances séries                                                                                                                                                                     | 127<br>128<br>129<br>130<br>130<br>131<br>132                                           |  |  |

|    | IV.3  | IV.2.3<br>IV.2.4                                         | IV.2.2.a Résultats électriques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 127<br>128<br>129<br>130<br>130<br>131<br>132<br>133                                    |  |  |

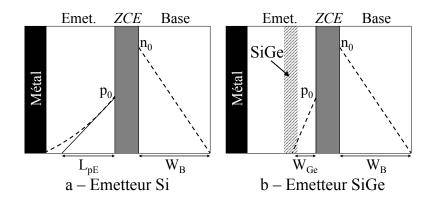

|    | IV.3  | IV.2.3 IV.2.4 Insertic                                   | IV.2.2.a Résultats électriques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 127<br>128<br>129<br>130<br>130<br>131<br>132<br>133<br>134                             |  |  |

|    | IV.3  | IV.2.3 IV.2.4 Insertic IV.3.1                            | IV.2.2.a Résultats électriques  IV.2.2.b Analyse SIMS  IV.2.2.c Mesures d'effet Hall  IV.2.2.d Interprétation – Suite de l'étude  Résultats obtenus avec un émetteur faiblement dopé  IV.2.3.a Résultats électriques  IV.2.3.b Problème d'augmentation des résistances séries  Perspectives  on de SiGe dans l'émetteur  Mise en œuvre                                                                                                                                                                                          | 127<br>128<br>129<br>130<br>131<br>132<br>133<br>134<br>134                             |  |  |

|    | IV.3  | IV.2.3 IV.2.4 Insertic IV.3.1                            | IV.2.2.a Résultats électriques IV.2.2.b Analyse SIMS IV.2.2.c Mesures d'effet Hall IV.2.2.d Interprétation – Suite de l'étude Résultats obtenus avec un émetteur faiblement dopé IV.2.3.a Résultats électriques IV.2.3.b Problème d'augmentation des résistances séries Perspectives On de SiGe dans l'émetteur Mise en œuvre Résultats électriques                                                                                                                                                                             | 127<br>128<br>129<br>130<br>130<br>131<br>132<br>133<br>134<br>134<br>135               |  |  |

|    | IV.3  | IV.2.3 IV.2.4 Insertic IV.3.1                            | IV.2.2.a Résultats électriques  IV.2.2.b Analyse SIMS  IV.2.2.c Mesures d'effet Hall  IV.2.2.d Interprétation – Suite de l'étude  Résultats obtenus avec un émetteur faiblement dopé  IV.2.3.a Résultats électriques  IV.2.3.b Problème d'augmentation des résistances séries  Perspectives  on de SiGe dans l'émetteur  Mise en œuvre  Résultats électriques  IV.3.2.a Résultats statiques                                                                                                                                     | 127<br>128<br>129<br>130<br>131<br>132<br>133<br>134<br>134<br>135                      |  |  |

|    |       | IV.2.3 IV.2.4 Insertic IV.3.1 IV.3.2                     | IV.2.2.a Résultats électriques IV.2.2.b Analyse SIMS IV.2.2.c Mesures d'effet Hall IV.2.2.d Interprétation – Suite de l'étude Résultats obtenus avec un émetteur faiblement dopé IV.2.3.a Résultats électriques IV.2.3.b Problème d'augmentation des résistances séries Perspectives On de SiGe dans l'émetteur Mise en œuvre Résultats électriques IV.3.2.a Résultats statiques IV.3.2.b Performances dynamiques                                                                                                               | 127<br>128<br>129<br>130<br>131<br>132<br>133<br>134<br>135<br>135<br>136               |  |  |

|    |       | IV.2.3 IV.2.4 Insertic IV.3.1 IV.3.2                     | IV.2.2.a Résultats électriques IV.2.2.b Analyse SIMS IV.2.2.c Mesures d'effet Hall IV.2.2.d Interprétation – Suite de l'étude Résultats obtenus avec un émetteur faiblement dopé IV.2.3.a Résultats électriques IV.2.3.b Problème d'augmentation des résistances séries Perspectives On de SiGe dans l'émetteur Mise en œuvre Résultats électriques IV.3.2.a Résultats statiques IV.3.2.b Performances dynamiques Conclusion sur l'insertion de Ge dans l'émetteur                                                              | 127<br>128<br>129<br>130<br>131<br>132<br>133<br>134<br>135<br>135<br>136<br>136        |  |  |

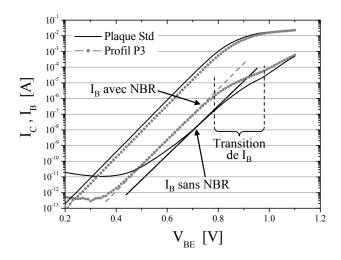

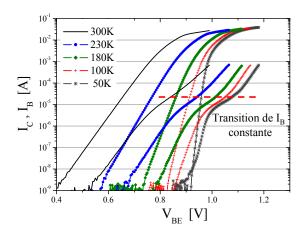

|    |       | IV.2.3 IV.2.4 Insertic IV.3.1 IV.3.2 IV.3.3 Recom IV.4.1 | IV.2.2.a Résultats électriques IV.2.2.b Analyse SIMS IV.2.2.c Mesures d'effet Hall IV.2.2.d Interprétation – Suite de l'étude Résultats obtenus avec un émetteur faiblement dopé IV.2.3.a Résultats électriques IV.2.3.b Problème d'augmentation des résistances séries Perspectives On de SiGe dans l'émetteur Mise en œuvre Résultats électriques IV.3.2.a Résultats statiques IV.3.2.b Performances dynamiques Conclusion sur l'insertion de Ge dans l'émetteur Ibinaison en base neutre                                     | 127<br>128<br>129<br>130<br>131<br>132<br>133<br>134<br>135<br>135<br>136<br>136<br>138 |  |  |

|    |       | IV.2.3 IV.2.4 Insertic IV.3.1 IV.3.2 IV.3.3 Recom IV.4.1 | IV.2.2.a Résultats électriques IV.2.2.b Analyse SIMS IV.2.2.c Mesures d'effet Hall IV.2.2.d Interprétation – Suite de l'étude Résultats obtenus avec un émetteur faiblement dopé IV.2.3.a Résultats électriques IV.2.3.b Problème d'augmentation des résistances séries Perspectives on de SiGe dans l'émetteur Mise en œuvre Résultats électriques IV.3.2.a Résultats statiques IV.3.2.b Performances dynamiques Conclusion sur l'insertion de Ge dans l'émetteur Ibinaison en base neutre Mise en œuvre Résultats électriques | 127<br>128<br>129<br>130<br>131<br>132<br>133<br>134<br>135<br>135<br>136<br>136<br>138 |  |  |

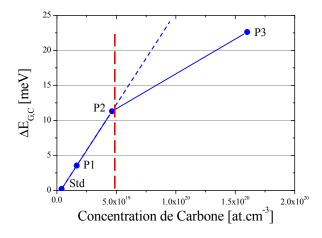

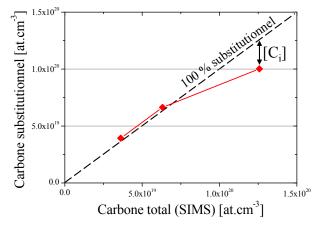

|              | IV 5                  | IV.4.6          | .5 Influence du carbone sur le gap du matériau |                                                             |     |  |  |

|--------------|-----------------------|-----------------|------------------------------------------------|-------------------------------------------------------------|-----|--|--|

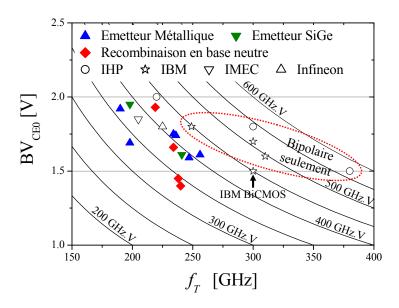

|              | 1 4.5                 | •               |                                                | ison des différentes méthodes                               |     |  |  |

|              |                       | IV.5.2          |                                                | ement par rapport à la concurrence                          |     |  |  |

|              |                       |                 |                                                | on / Perspectives                                           |     |  |  |

| $\mathbf{V}$ | Influ                 | ence de         | la tempé                                       | rature                                                      | 149 |  |  |

|              | V.1                   |                 | _                                              |                                                             | 149 |  |  |

|              | V.2                   | Étude d         | le l'auto-é                                    | chauffement                                                 | 149 |  |  |

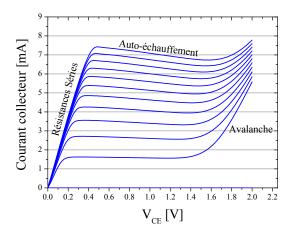

|              |                       | V.2.1           | Limitatio                                      | ns induites par l'auto-échauffement                         | 149 |  |  |

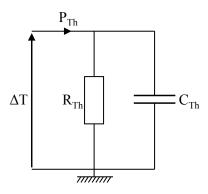

|              |                       | V.2.2           | Extractio                                      | n de la résistance thermique                                | 150 |  |  |

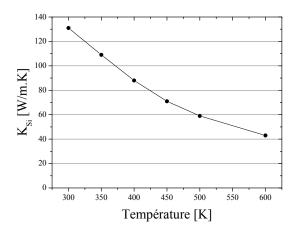

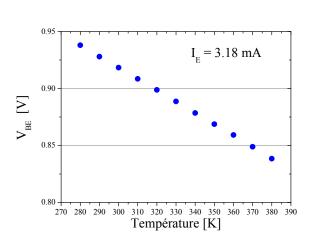

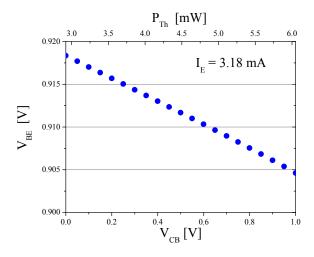

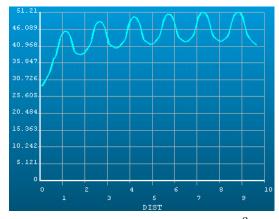

|              |                       |                 | V.2.2.a                                        | Extraction en régime continu                                | 150 |  |  |

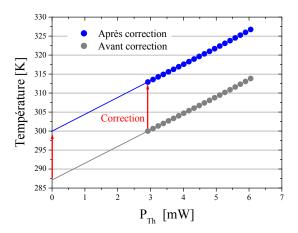

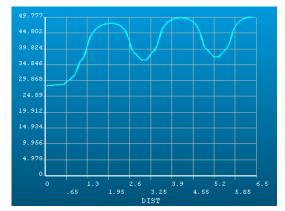

|              |                       |                 | V.2.2.b                                        | Extraction en régime pulsé                                  | 153 |  |  |

|              |                       |                 | V.2.2.c                                        | Comparaison des différentes méthodes                        | 154 |  |  |

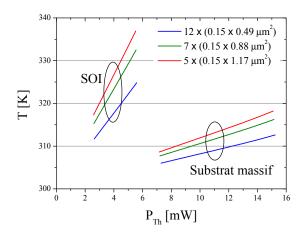

|              |                       | V.2.3           | Réduction                                      | n de l'auto-échauffement par des variantes technologiques   |     |  |  |

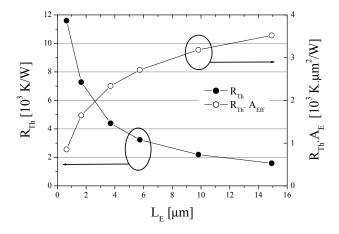

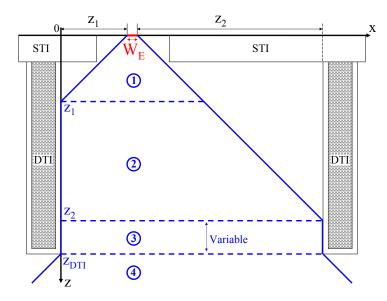

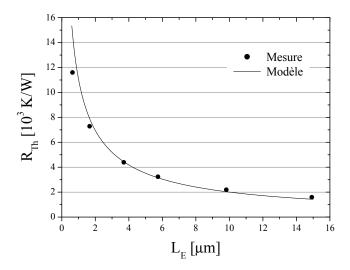

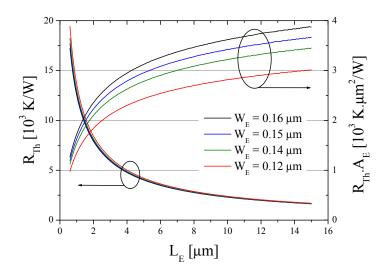

|              |                       |                 | V.2.3.a                                        | Influence de la dimension de l'émetteur                     |     |  |  |

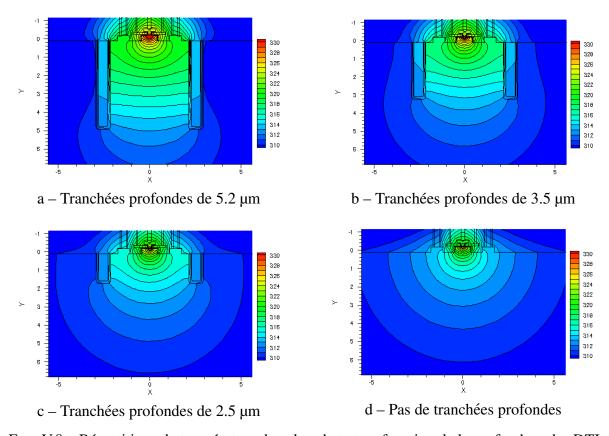

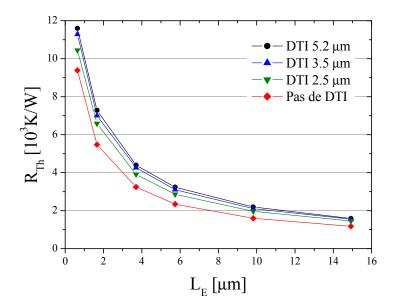

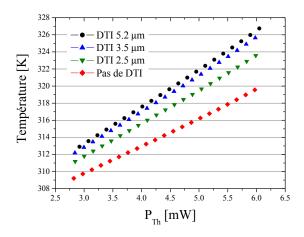

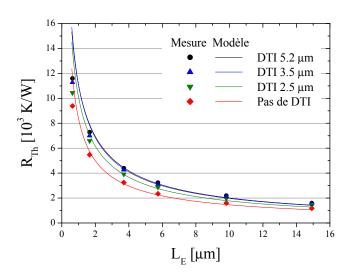

|              |                       |                 | V.2.3.b                                        | Effet des tranchées profondes d'isolation                   |     |  |  |

|              |                       |                 | V.2.3.c                                        | Émetteurs fractionnés ou multi-doigts                       |     |  |  |

|              |                       |                 | V.2.3.d                                        | Effet du type de substrat                                   |     |  |  |

|              |                       | ,               | V.2.3.e                                        | Élaboration d'un modèle simple                              |     |  |  |

|              | V.3                   |                 |                                                | basse température                                           |     |  |  |

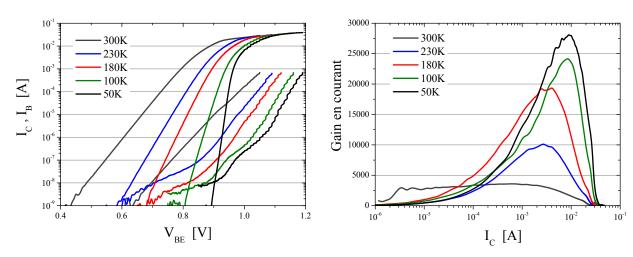

|              |                       | V.3.1           |                                                | tion des paramètres statiques à basse température           |     |  |  |

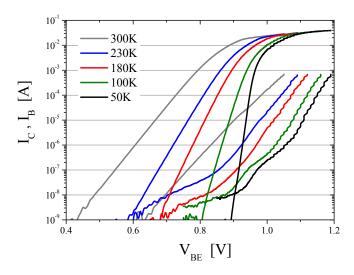

|              |                       |                 | V.3.1.a                                        | Evolution des niveaux de courant                            |     |  |  |

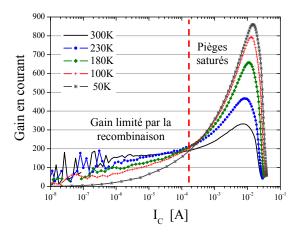

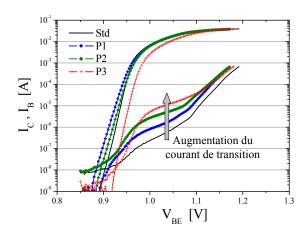

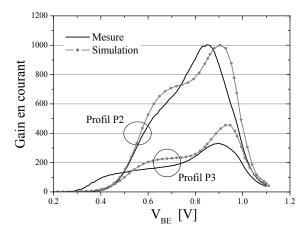

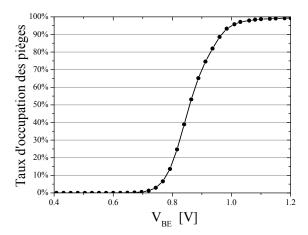

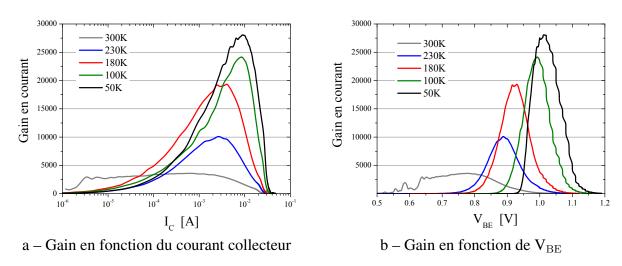

|              |                       |                 | V.3.1.b                                        | Variation du gain en courant avec la température            |     |  |  |

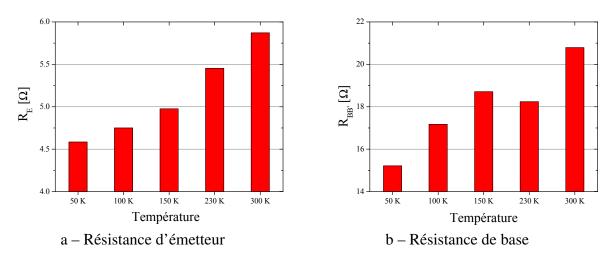

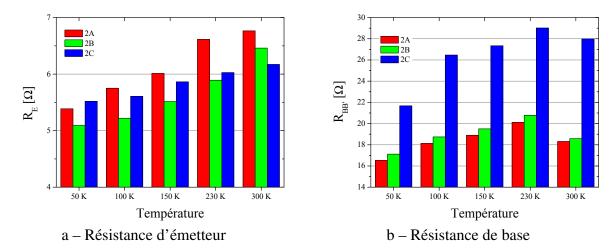

|              |                       |                 | V.3.1.c                                        | Évolution des autres paramètres statiques                   |     |  |  |

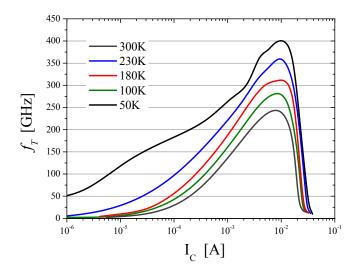

|              |                       | V.3.2           |                                                | nces dynamiques à basse température                         |     |  |  |

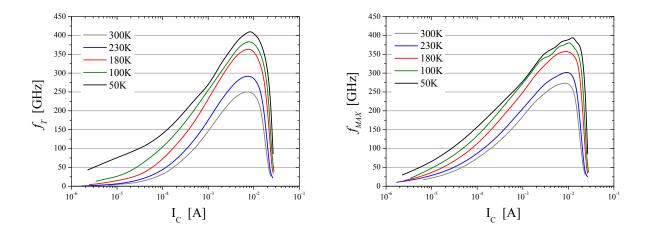

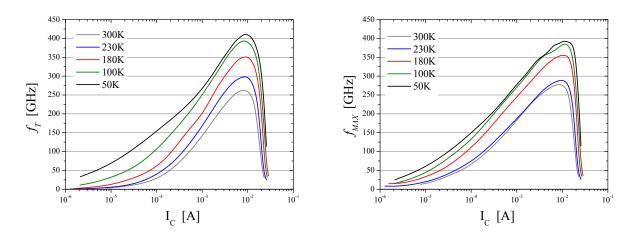

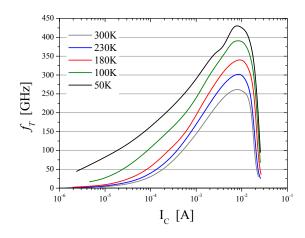

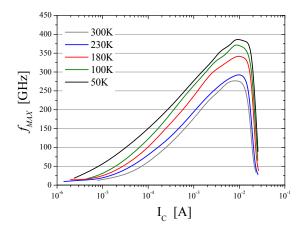

|              |                       |                 | V.3.2.a                                        | Fréquences $f_T$ et $f_{MAX}$ aux températures cryogéniques |     |  |  |

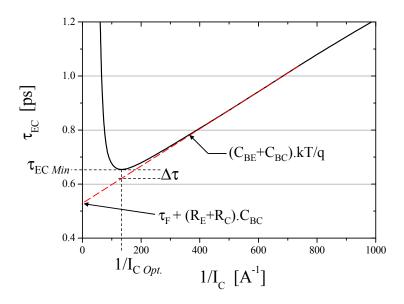

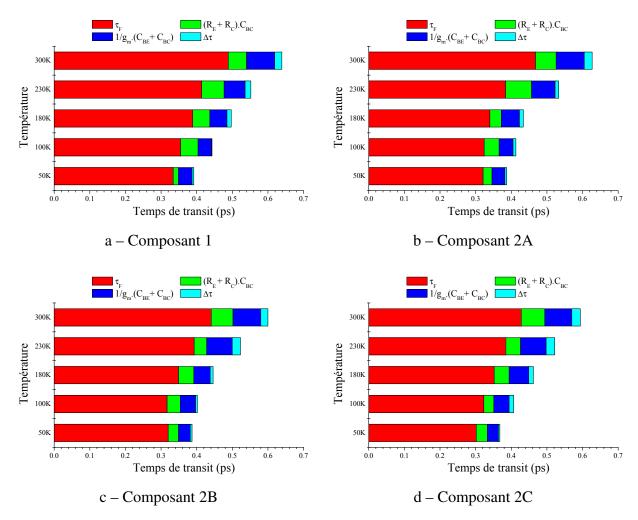

|              |                       |                 | V.3.2.b                                        | Étude des temps de transit                                  |     |  |  |

|              | V.4                   | V.3.3<br>Conclu | •                                              | de l'étude cryogénique                                      |     |  |  |

| Cor          | nclus                 | ion gén         |                                                | •                                                           | 177 |  |  |

|              |                       | C               |                                                |                                                             |     |  |  |

| Pub          | olicat                | tions de        | l'auteur                                       |                                                             | 181 |  |  |

| Réf          | éren                  | ces bibli       | iographiq                                      | ues                                                         | 183 |  |  |

| List         | te de                 | s figures       | S                                              |                                                             | 193 |  |  |

| List         | iste des tableaux 201 |                 |                                                |                                                             |     |  |  |

## Introduction

Jusqu'à il y a une dizaine d'années, l'industrie de la microélectronique était cloisonnée : D'un côté, on trouvait les circuits logiques complémentaires, représentant l'écrasante majorité du marché, principalement pour des applications logiques comme les microprocesseurs. Le composant sur lequel reposent ces technologies, le transistor MOSFET (Metal Oxide Semiconductor Field Effect Transistor), est en effet facilement réalisable à partir d'un substrat en silicium et propice à de forts volumes de production en milieu industriel, ce qui permet de gros volumes de production à des coûts relativement faibles. Ceci explique l'incroyable essor des technologies silicium CMOS (Complementary MOS) dans la seconde moité du XX<sup>e</sup> siècle, prenant ainsi l'avantage sur les technologies utilisant des transistors bipolaires à homojonction (logique TTL notamment).

D'un autre côté, les circuits III-V (GaAs, GaN, InP, ou alliages plus complexes...) permettent d'adresser des applications analogiques et hyper-fréquences en utilisant des transistors bipolaires à hétérojonction, des MESFET (MEtal Semiconductor Field Effect Transistor) ou des HEMT (High Electron Mobility Transistor). Utilisés dans le domaine des télécommunications ou en environnement militaire pour la détection et le guidage, ces circuits sont produits en plus faibles quantités, et à des coûts bien supérieurs à ceux d'un circuit CMOS. Le prix élevé des technologies III-V est d'une part lié au faible volume de production, et d'autre part à la limitation de la taille du substrat ainsi qu'au coût de celui-ci, bien supérieur au coût d'un substrat silicium. Les transistors bipolaires rapides développés pour les applications de télécommunication et de détection étaient historiquement fabriqués en matériaux III-V. Il est en effet possible de modifier la structure de bandes du composant et de créer ainsi le profil favorable à l'obtention des meilleures performances dynamiques. Les fréquences obtenues avec un transistor bipolaire InP s'élèvent au dessus du THz. Ces composants III-V sont encore très utilisés pour les applications millimétriques ou bien nécessitant de fortes puissances, car les propriétés de transport des électrons sont très bonnes dans ce type de matériau, permettant d'excellentes performances.

Cependant, la diversification des applications grand public entraîne des contraintes de coût, d'encombrement et de consommation de plus en plus importantes. On a vu apparaître la nécessité de faire cohabiter des circuits logiques avec des circuits analogiques ou hyperfréquences sur une même puce, notamment pour les applications de communication sans fil.

A mesure de l'amélioration des performances dynamiques des circuits BiCMOS, les composants III-V ont donc été remplacés petit à petit par des circuits tout silicium, ce qui permet d'augmenter l'intégration et de réduire les coûts de fabrication. Un nouveau type de technologie a donc été développé pour répondre aux besoins des applications hautes fréquences à destination du grand public. Les technologies dites BiCMOS utilisent des transistors bipolaires et des transistors MOS, et allient ainsi les avantages des deux types de composants : Fortes fréquences de fonctionnement et faible bruit pour le premier, haute densité d'intégration et faible consommation pour le second.

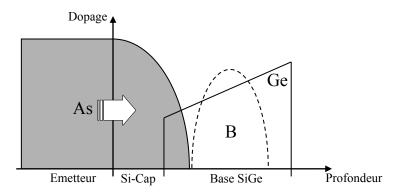

Historiquement, les technologies BiCMOS employaient des transistors bipolaires tout silicium. Il y a une dizaine d'années, l'introduction du Germanium dans la base du composant 2 INTRODUCTION

a permis l'ingénierie de la structure de bandes. Les performances des transistors bipolaires se sont donc rapidement améliorées grâce aux progrès réalisés sur les matériaux. Le SiGe offre à l'heure actuelle une maturité de procédé, un niveau d'intégration et des rendements proches de ce qui est couramment obtenu pour le silicium. Les technologies utilisant du SiGe commencent à replacer les matériaux III-V pour la partie réception des systèmes de communication dans le domaine RF-basse fréquence; la partie émission utilisant des amplificateurs de puissance restant encore l'apanage des composants III-V, ainsi que le domaine des très hautes fréquences.

C'est dans le cadre du développement de technologies BiCMOS que s'inscrit mon travail de thèse. Le but de l'étude est la réalisation et l'analyse de transistors bipolaires rapides réalisés en anticipation des technologies BiCMOS futures. Cette thèse a pour objectif de mettre en avant les limitations existant dans la structure de transistor bipolaire la plus récente, et de déboucher sur des solutions performantes et maîtrisables en milieu industriel afin d'améliorer les performances des composants. Pour cela, nous disposons des procédés de fabrication avancés disponibles à STMicroelectronics, ainsi que des techniques et méthodes d'analyse expérimentales de l'IEF. Cette thèse a également pour but de dresser un tableau de perspectives pour l'optimisation ultérieure du composant.

Dans un premier temps, nous rappelons la théorie de fonctionnement du transistor bipolaire. Nous mettons en avant les propriétés du matériau SiGe, et nous présentons les améliorations qu'apporte ce matériau sur le transistor bipolaire. Le fonctionnement théorique du TBH est ensuite décrit, en régime statique et dynamique. Nous détaillons les outils d'analyse expérimentale (caractérisation physique et électrique), et notamment l'intérêt de l'analyse du composant à basses températures.

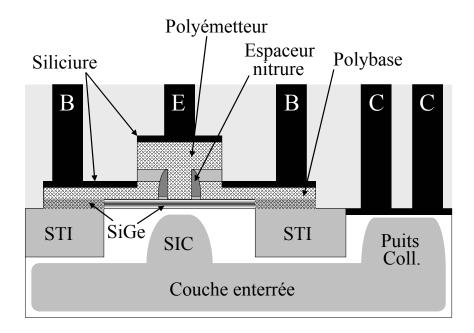

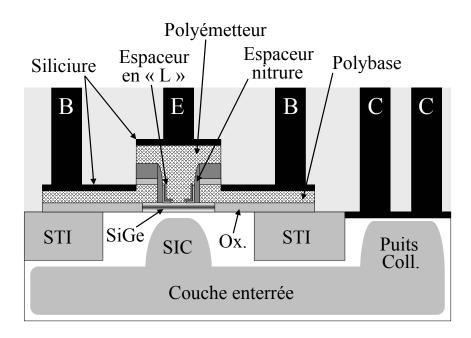

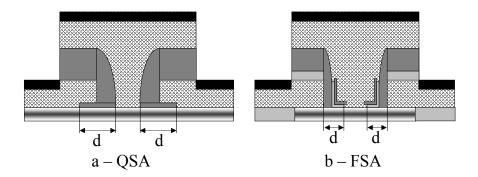

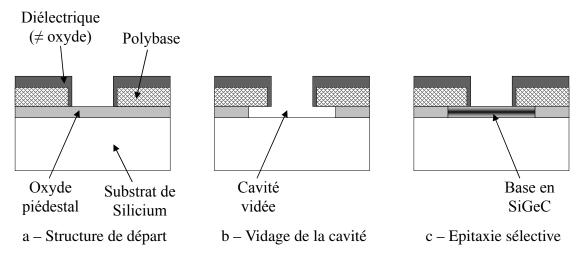

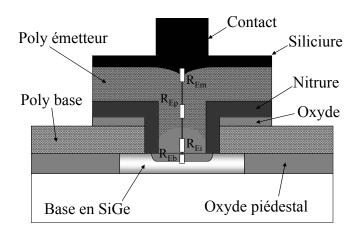

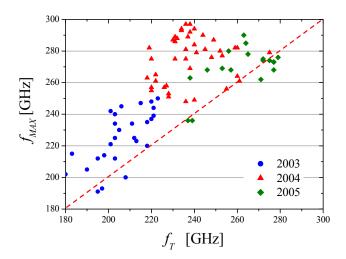

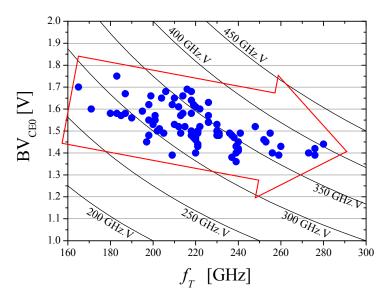

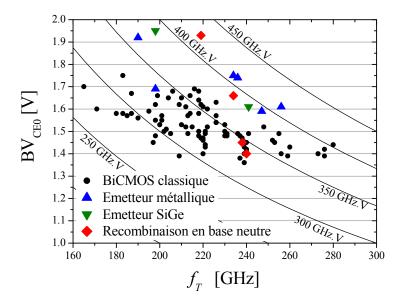

Au chapitre II, nous détaillons les procédés de fabrication des transistors bipolaires à hétérojonction Si/SiGe. Après un bref passage en revue des structures développées par le passé, nous présentons le choix d'architecture qui s'offrait à nous pour les futures technologies BiCMOS. Les raisons ayant mené à la structure actuelle sont explicitées, et le procédé de fabrication des composants est décrit en détail. En fin de ce chapitre, nous proposons de situer les performances des transistors bipolaires de ST dans une analyse de l'état de l'art. Ainsi, les architectures et les résultats d'autres acteurs du marché de la microélectronique sont présentés. Cette analyse permet de mettre en avant les avantages et points faibles de chaque structure.

Le chapitre III traite de l'optimisation dite « conventionnelle » des transistors bipolaires qui a permis d'atteindre les performances présentées dans le chapitre précédent. Nous étudions tout d'abord des améliorations apportées par l'optimisation du profil vertical de chaque partie du composant (émetteur, base et collecteur), et présentons ensuite l'optimisation de l'extension latérale du composant. Une synthèse de cette optimisation classique est ensuite réalisée, en résumant l'évolution des performances obtenues aux cours des trois ans qu'a durée cette étude. Nous terminons le chapitre par des considérations sur l'intégration de ces composants pour réaliser des circuits rapides.

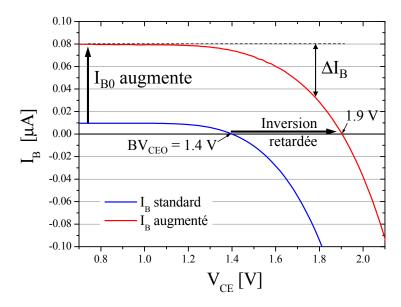

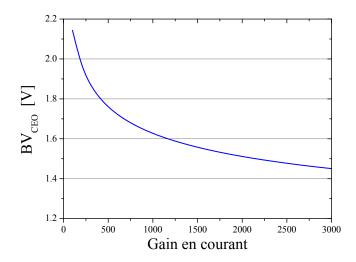

Le chapitre sur l'optimisation conventionnelle a mis l'accent sur le compromis existant entre les performances dynamiques et la tenue en tension du transistor. Le chapitre IV présente trois procédés innovants permettant de repousser ce compromis en augmentant le courant de base du transistor. Chaque procédé offre ainsi la possibilité d'améliorer la tenue en tension du composant, par une variante technologique appropriée, permettant de modifier la comportement du composant. Ainsi, nous étudierons successivement les améliorations apportées par le procédé émetteur métallique, l'insertion de Ge dans l'émetteur, et l'augmentation de la recombinaison

INTRODUCTION 3

dans la base neutre par l'ajout de fortes doses de carbone. Chaque procédé est décrit, ainsi que ses avantages et ses inconvénients, et nous replaçons ensuite les performances obtenues par rapport à l'état de l'art.

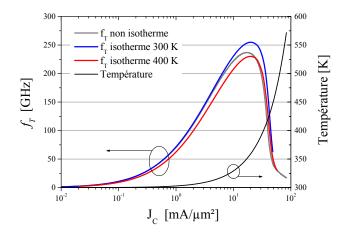

Le dernier chapitre a pour objet l'étude du transistor bipolaire en fonction de la température. La première partie du chapitre porte sur l'auto-échauffement du composant. Le chapitre III a en effet mis en avant la possibilité d'améliorer les performances grâce à l'augmentation de la densité de courant, mais ceci a pour effet néfaste de générer beaucoup de chaleur. L'élévation de température interne, inhérente au fonctionnement du transistor apparaît donc comme une limitation des performances. Après avoir mis en place une méthode pour caractériser cet auto-échauffement, nous présentons les techniques existantes pour réduire la montée en température. Le second point porte sur l'analyse cryogénique du transistor bipolaire. En effet, les performances dynamiques sont améliorées lorsqu'on descend à des températures très basses, ce qui permet d'en tirer des informations importantes sur la capacité de la structure à évoluer vers des performances ultimes. Nous montrerons à ce titre que la principale limitation du transistor bipolaire se situe dans la partie intrinsèque.

Nous conclurons cette thèse par une synthèse des résultats obtenus, et nous évoquerons des perspectives quant à l'évolution future du transistor bipolaire à hétérojonction Si/SiGe pour les technologies BiCMOS à venir.

4 INTRODUCTION

## **Chapitre I**

# Le transistor bipolaire à hétérojonction Si / SiGeC

## I.1 Introduction sur le transistor bipolaire

Le transistor bipolaire a été inventé en 1948 par Bardeen et Brattain, et sa théorie a été élaborée en 1949 par Shockley. Depuis 1951, date du premier transistor à jonction, les développements poussés, tant sur les matériaux que sur les dimensions du dispositif, ont permis d'atteindre des performances records, largement utilisées dans le domaine des télécommunications ou dans des applications nécessitant de fortes puissances.

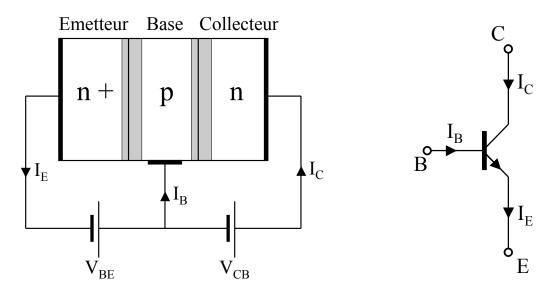

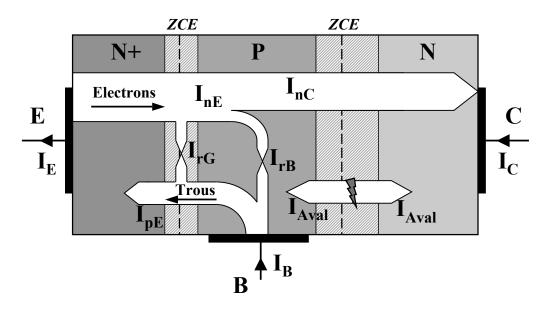

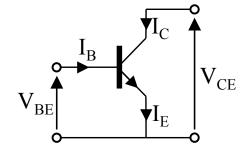

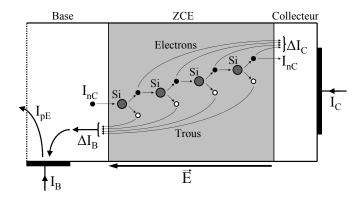

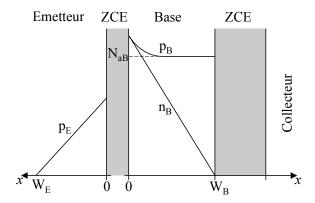

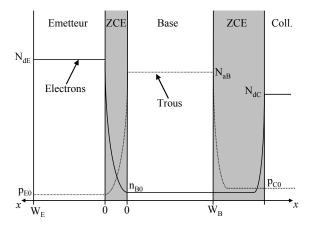

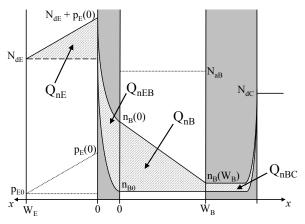

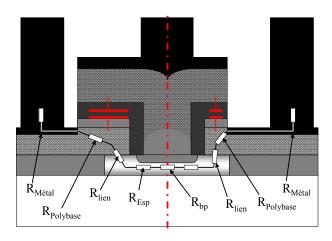

Le transistor bipolaire est un composant électronique composé de trois zones semiconductrices successives dopées dans les deux configurations possibles NPN ou PNP, appelées successivement *émetteur*, *base* et *collecteur*. Il s'agit donc de deux jonctions PN tête-bêche ayant une région en commun comme représenté sur la figure I.1.

FIG. I.1 – Schéma d'un transistor bipolaire NPN. En noir : contacts métalliques; zones grisées : zones de charge d'espace des jonctions E/B et B/C.

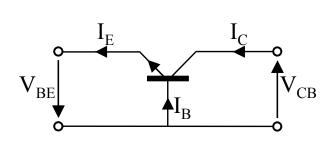

FIG. I.2 – Représentation symbolique du NPN utilisée dans les schémas électriques.

Le transistor NPN est le plus utilisé pour les applications nécessitant des circuits rapides, car la conduction repose principalement sur les électrons, qui sont plus rapides que les trous. Le transistor considéré tout au long de cette thèse est le transistor NPN, c'est celui qui a fait

l'objet des développements les plus poussés au cours des dernières années. Il faut cependant noter que les différents courants du transistor bipolaire font intervenir les deux types de porteurs (électrons *et* trous), contrairement aux composants à effet de champ, où un seul type de porteur est sollicité.

Le transistor bipolaire peut être polarisé de 4 manières différentes, qui déterminent chacune un mode de fonctionnement. Les différents modes de fonctionnement du transistor bipolaire sont :

- Mode direct : Jonction émetteur/base en direct et base/collecteur en inverse.

- Mode saturé : Jonction émetteur/base en direct et base/collecteur en direct.

- Mode inverse : Jonction émetteur/base en inverse et base/collecteur en direct.

- Mode bloqué : Jonction émetteur/base en inverse et base/collecteur en inverse.

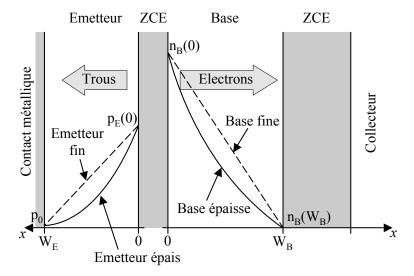

Le mode le plus couramment utilisé dans les applications analogiques et radio-fréquences est le mode direct. C'est la proximité des deux jonctions du composant qui est à la base de l'*effet transistor*: Pour obtenir un bon fonctionnement du composant, il faut que les porteurs minoritaires injectés dans la base par l'émetteur, les électrons, parviennent jusqu'à la jonction base/collecteur. Ceci implique l'emploi de bases assez fines pour éviter la recombinaison en volume, il est impératif que la longueur de diffusion des électrons soit supérieure à l'épaisseur de la base neutre  $W_{\rm B}$ .

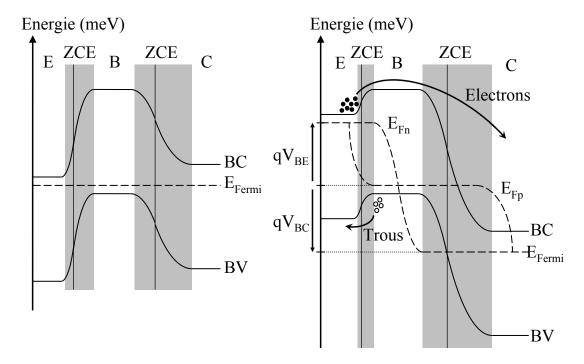

- a) Au repos (polarisation nulle)

- b) Sous polarisation normale directe

FIG. I.3 – Diagramme de bandes d'un transistor bipolaire NPN : a – au repos et b – en régime de fonctionnement normal. L'abaissement des barrières pour les électrons et pour les trous autorise le passage du courant.

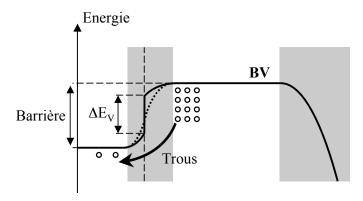

Le profil de bandes d'un transistor NPN au repos est présenté sur la figure I.3–a. Lorsque la jonction émetteur/base est polarisée en direct, les barrières s'abaissent pour les trous et les électrons, autorisant ainsi le passage du courant. Les électrons diffusent de la base vers le collecteur, et sont happés par la zone de charge d'espace (ZCE) base/collecteur. La polarisation inverse de cette jonction base/collecteur sert à créer un très fort champ électrique qui accélère les électrons (figure I.3–b).

Le transistor bipolaire est un composant dit actif qui se comporte comme une source de courant commandée en tension. La jonction émetteur/base contrôle le courant principal du transistor. Dans le cas d'un transistor à homojonction, il faut que la jonction E/B soit fortement dissymétrique (i.e. dopage d'émetteur très supérieur au dopage de base) pour que la majorité des porteurs injectés soient des électrons, permettant ainsi d'obtenir une efficacité d'injection maximale. La quantité de trous injectés dans l'émetteur sera très faible en regard des électrons injectés dans la base.

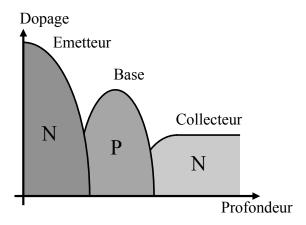

Ces électrons injectés dans la base atteignent la jonction base/collecteur par un mécanisme de diffusion. Le courant collecteur dépend donc du gradient d'électrons dans la base. Dans un transistor idéal le courant ne doit pas varier lorsque la polarisation de la jonction base/collecteur varie. Afin de garantir cet effet, il ne faut pas que le gradient d'électrons dépende de la tension B/C. Ceci est possible en assurant un dopage de base très supérieur à celui du collecteur. On en déduit le profil de dopage générique d'un transistor représenté sur la figure I.4 suivante :

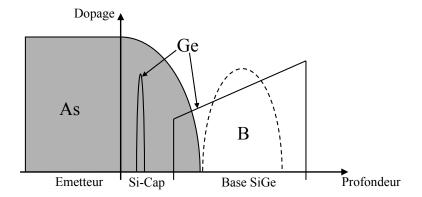

FIG. I.4 – Profil de dopage générique d'un transistor bipolaire

## I.2 L'alliage Silicium-Germanium